I am delighted to share my technical insights into RISC-V in this article to inspire and prepare the next generation of chip designers for the future of the open era of computing. If you understand how we build complex electronic devices like desktops and smartphones using processors, you would be more interested in learning and… Read More

Semiconductor Intellectual Property

High-End Interconnect IP Forecast 2022 to 2026

The Interface IP market has grown with 21% CAGR from 2017 to 2021 and we review the part of this market restricted to the high-end of PCIe, DDR, Ethernet and D2D IP made of PHY and controller targeting the most advanced technology nodes and latest protocol release. We will show that an IP vendor focusing investment on the high-end interconnect… Read More

Integration Methodology of High-End SerDes IP into FPGAs

Over the last couple of decades, the electronics communications industry has been a significant driver behind the growth of the FPGA market and continues on. A major reason behind this is the many different high-speed interfaces built into FPGAs to support a variety of communications standards/protocols. The underlying input-output… Read More

Selecting a flash controller for storage reliability

Flash memory cards and solid-state drives (SSDs) provide high-performance storage in many devices and systems today. While the flash chips inside cards and SSDs provide raw capacity and performance, they must be combined with an intelligent flash controller to achieve the reliability system designers and consumers need. … Read More

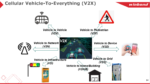

MIPI in the Car – Transport From Sensors to Compute

I’ve written on and off about sensors, ML inference of the output of those sensors and the application of both in modern cars. Neither ADAS nor autonomous/semi-autonomous driving would be possible without these. But until now I have never covered the transport between sensors and the compute that safely turns what they produce… Read More

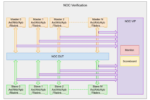

Truechip Introduces Automation Products – NoC Verification and NoC Performance

While Truechip has established itself as a global provider of verification IP (VIP) solutions, they are always on the lookout for strategic IP needs from their customer base. Over the last several years, a solid market for Network-on-Chip (NoC) IP has grown, driven by the need to rapidly move data across a chip. Concurrently, the… Read More

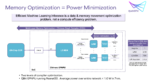

Slashing Power in Wearables. The Next Step

In wearables and hearables, low power is king. Earbuds for example still only manage a half-day active use before we need to recharge. Half a day falls short of truly convenient for most of us – a full day would be much better, allowing for overnight recharge. Physics limits battery sizes so system designers must look to SoC architectures… Read More

Quadric’s Chimera GPNPU IP Blends NPU and DSP to Create a New Category of Hybrid SoC Processor

Performance, Power and Area (PPA) are the commonly touted metrics in the semiconductor industry placing PPA among the most widely used acronyms relating to chip development. And rightly so as these three metrics greatly impact all electronic products that are developed. The degree of impact depends of course on the specific … Read More

Flash Memory Market Ushered in Fierce Competition with the Digitalization of Electric Vehicles

Governments worldwide have been paying close attention to alternative energy vehicles recently. Many have launched related electric vehicle subsidy policies, accelerating global sales over recent years.

In 2021 at IAA Mobility in Munich, Germany, many major car manufacturers, including Porsche, showcased their all-electric… Read More

The Corellium Experience Moves to EDA

Bill Neifert invited me to join him on Zoom recently to talk about his move to Corellium, a company known within the DevSecOps (development, security, operations) market. Developers and security groups use its virtualization technology to build, test, and secure mobile and IoT apps, firmware, and hardware.

Not knowing much … Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center