If you have bought a Samsung Gear S2 smartwatch for Christmas, you certainly didn’t open it to do a teardown. Chipworks did it and have shared the results: Qualcomm is the big winner here with five different chips: Snapdragon 400 as the main CPU of the system, the RF transceiver, the audio codec, the power and the baseband processor… Read More

Semiconductor Intellectual Property

Semiconductors Future Hinges on a Single Pillar

A unique phenomenon has started manifesting itself under the slew of mergers and acquisitions this year in the semiconductor landscape. This phenomenon is bound to intensify in the near future and would positions itself as a key factor for the future of the semiconductor industry. The winners and losers in the game would be determined… Read More

How Not To Be Incoherent

The advantage of working with cache memory is the great boost in performance you can get from working with a local high-speed copy of chunks of data from main memory. The downside is that you are messing with a copy; if another processor happens to be working in a similar area, there is a danger you can get out of sync when reading and writing… Read More

mbed OS abstraction battles IoT hyperfragmentation

In the days of bit banging and single-threaded loops, programming a microcontroller meant grabbing a C compiler (or even before that, an assembler) and some libraries and writing bare metal code. High performance networking and multi-tasking was usually the purview of heavier real-time operating systems (RTOS) or, if an MMU… Read More

Networking through Dark Silicon Power Islands

For decades, tracing back to the days of Deming, the way to tackle complex engineering problems has been the pareto chart. Charting conditions and their contribution to the problem leads to mitigation priorities.

In the case of SoC power management, the old school pareto chart said the processor core was the biggest power hog and… Read More

DSP gives Project Tango a power dip

Google’s Project Tango is a prime example of a sophisticated application pushing the boundaries of what is possible within the power envelope of a mobile device. Its objective is to combine 3D motion tracking with depth sensing to understand how a device is moving and gauge its surroundings precisely.… Read More

HDCP 2.2, Root of Trust, Industry’s First SHA-3 Security IP from Synopsys

Did you know that by 2020 90% of cars will be connected to Internet? Great, but today, there are already more than 100 car models affected with security flaws (Source: theguardian.com, 2015). That 320 apps are installed on average smartphone device? It would be a complete success, but 43% of Android devices allow installation of… Read More

How Wireless Modem IP is Aiding Roadmap to 5G Chipsets

The semiconductor industry is steadily charting its course toward 5G chipsets with the availability of extremely complex system-on-chip (SoC) designs that support the surge of data traffic over next-generation wireless networks. Take Blu Wireless Technology, for instance, the IP supplier from Britain that is using the Arteris… Read More

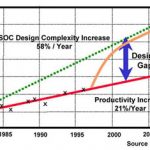

How to Solve the Business Gap in SEMI Industry?

This white paper about Cadence innovative mixed-signal IP concept “Cadence Multi-Link PHY IP (SerDes, Analog Front-end, and DDR) to Design SoC Platform breaking the “Business Gap” on 14/16FF” describe the problem, the emergence of a “business gap” linked with incredibly high development cost when targeting most advanced … Read More

Slinging Stones at the Data Center Semi Goliaths

For those not aware, there is quite a battle brewing in data center wired communication segment (across which most wireless data traffic traverses). A primary impetus driving the competitive positioning is the recent commercial availability of single lane 25 Gbps serdes (serializer / deserializer) channels in 28 nm CMOS from… Read More

Silicon Insurance: Why eFPGA is Cheaper Than a Respin — and Why It Matters in the Intel 18A Era