You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

WP_Term Object

(

[term_id] => 178

[name] => IP

[slug] => ip

[term_group] => 0

[term_taxonomy_id] => 178

[taxonomy] => category

[description] => Semiconductor Intellectual Property

[parent] => 0

[count] => 1993

[filter] => raw

[cat_ID] => 178

[category_count] => 1993

[category_description] => Semiconductor Intellectual Property

[cat_name] => IP

[category_nicename] => ip

[category_parent] => 0

[is_post] =>

)

Since its formation just last year, SiFive has been riding the RISC-V rocket from purely academic interest to first commercialization. In an exclusive discussion, I talked with CEO Stefan Dyckerhoff and VP of Product and Business Development Jack Kang about their progress so far and what may be coming next.

Previously, I covered… Read More

Machine Learning is at the hype peak, according with Gartner’s August 2016 Hype Cycle for Emerging Technologies. The demand for vision processor IP is strong in smartphone, automotive and consumer electronics segments. ASSP based solutions can make the job, but how can OEM create differentiation, control their destiny and … Read More

All the hubbub about FPGA-accelerated servers prompts a big question about cache coherency. Performance gains from external acceleration hardware can be wiped out if the system CPU cluster is frequently taking hits from cache misses after data is worked on by an accelerator.

ARM’s latest third-generation CoreLink CMN-600 … Read More

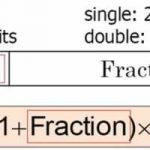

Floating-point computation has been a staple of mainframe, minicomputer, supercomputer, workstation, and PC platforms for decades. Almost all modern microprocessor IP supports the IEEE 754 floating-point standard. Embedded design, for reasons of power and area and thereby cost, often eschews floating-point hardware… Read More

Once a year, during the TSMC’s Open Innovation Platform (OIP) Forum you can expect to see cutting edge technical achievements by TSMC and their partners. This year was no exception, with Open-Silicon presenting its accomplishments in implementing an HBM reference design in 16nm. It’s well understood that HBM offers huge benefits… Read More

Cache evolved when the world was all about homogeneous processing and slow and expensive shared memory. Now, compute is just part of the problem – devices need to handle display, connectivity, storage, and other tasks, all at the same time. Different, heterogeneous cores handle different workflows in the modern SoC, and the burden… Read More

Design starts are the lifeblood of the semiconductor industry which is why we have been following the eSilicon STAR Platform since its introduction with great anticipation. The STAR platform was first launched about three years ago. Today, there are over 1,300 registered STAR users in 52 countries around the world.

The ASIC business… Read More

It is a busy month for book signings but it is a pleasure to do it for the greater good of the semiconductor industry. It really is an honor to meet the people who keep our electronic devices on the leading edge of technology, absolutely.

The Linley Processor Conference is on September 27[SUP]th[/SUP]and 28[SUP]th[/SUP] at the Hyatt… Read More

As most of you know SemiWiki published a book which is a really nice history of the fabless semiconductor ecosystem. Thousands of people have copies, we have received many compliments on it, and we are very proud. As a thank you to all SemiWiki members I would like to offer a free electronic version of the book (PDF). You can access it… Read More

This is the first in a series of CEO interviews and I thought semiconductor IP would be a great place to start. Xerxes Wania is the President and CEO of Sidense, a leading developer of Non-Volatile Memory (NVM) One-Time Programmable (OTP) IP cores. Sidense has been a part of SemiWiki since 2013 so we know them quite well. I hope the rest… Read More

Silicon Insurance: Why eFPGA is Cheaper Than a Respin — and Why It Matters in the Intel 18A Era