You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

WP_Term Object

(

[term_id] => 14

[name] => Synopsys

[slug] => synopsys

[term_group] => 0

[term_taxonomy_id] => 14

[taxonomy] => category

[description] =>

[parent] => 157

[count] => 784

[filter] => raw

[cat_ID] => 14

[category_count] => 784

[category_description] =>

[cat_name] => Synopsys

[category_nicename] => synopsys

[category_parent] => 157

[is_post] =>

)

WP_Term Object

(

[term_id] => 14

[name] => Synopsys

[slug] => synopsys

[term_group] => 0

[term_taxonomy_id] => 14

[taxonomy] => category

[description] =>

[parent] => 157

[count] => 784

[filter] => raw

[cat_ID] => 14

[category_count] => 784

[category_description] =>

[cat_name] => Synopsys

[category_nicename] => synopsys

[category_parent] => 157

[is_post] =>

)

“We intend to grow revenue 14% to 15%, continue to drive notable ops margin expansion and aim for approximately 16% non-GAAP earnings per share growth.”

Synopsys, Inc. (NASDAQ:SNPS) Q4 2022 Earnings Call Transcript

Synopsys is the EDA bellwether since they report early and are the #1 EDA and #1 IP company. In addition to crossing… Read More

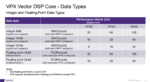

Configurable processors are hot now, in no small part thanks to RISC-V. Which is an ISA rather than a processor, but let’s not quibble. Arm followed with configurability in Cortex-X. Both were considerably preceded (a couple of decades) by Synopsys ARC® RISC CPUs and CEVA DSPs. Each stressed configurability as a differentiator… Read More

New EDA product launches are always an exciting time, and I could hear the energy and optimism from the voice of Manoj Chacko at Synopsys in our Zoom call about Synopsys PrimeClosure. During the physical implementation phase for IC designs there’s a big challenge to reach timing closure, and with advanced nodes the number… Read More

Over the last few years, the design of application-specific ICs as well as high-performance CPUs and other complex ICs has hit a proverbial wall. This wall is built from several issues: first, chip sizes have grown so large that they can fill the entire mask reticle and that could limit future growth. Second, the large chip size impacts… Read More

SiMa.ai just announced that they achieved first silicon success on their new MLSoC, for AI applications at the edge, using Synopsys’ design, verification, IP and design services solutions. Notably this design includes the Synopsys ARC® EV74 processor (among other IP) for vision processing. SiMa.ai claim their platform, now… Read More

Verification has long been the most time-consuming and often resource-intensive part of chip development. Building out the infrastructure to tackle verification can be a costly endeavor, however. Emerging and even well-established semiconductor companies must weigh the Cost-of-Results (COR) against Time-to-Results

…

Read More

Synopsys Fusion Compiler offers advanced optimizations to achieve the best PPA (power, performance, area) on today’s high-performance cores and interconnect designs. However, advanced transformation techniques available in synthesis such as retiming, multi-bit registers, advanced datapath optimizations, etc. are

…

Read More

I consider Dr. Aart de Geus one of the founding fathers of EDA and one of the most interesting people in the semiconductor industry. So it is not a surprise that Aart was chosen to attend the CHIPs Act signing at the White House.

Here is his current corporate bio:

Since co-founding Synopsys in 1986, Dr. Aart de Geus has expanded Synopsys… Read More

The design and characterization of RF circuits is a complex process that requires an RF designer to overcome a variety of challenges. Not only do they face the complexities posed by advanced semiconductor processes and the need to meet the demanding requirements of modern wireless standards, designers must also account for electromagnetic… Read More

Whether we realize it or not, everyday applications we use depend on data gathered by sensors. We can bet that pretty much every application uses at least a couple of different types of sensors, if not more. That is because different types of sensors are better suited to collect data depending on the application, the environment … Read More