Analog IC designers are gradually adopting what digital IC designers have been doing for years, metric driven verification. When you talk with analog designers about their methodology and approach, you hear terms like artisan being used which implies mostly a manually-oriented methodology. Thanks to automation from EDA companies,… Read More

IoT begets silicon, interoperability, and standards

The Internet of Things is on every technology mind these days, but what does it mean for the EDA community? Dennis Brophy of Mentor Graphics says the billions of things we are hearing about will not happen unless we find a way to build a lot more things, efficient things, and connected things. He has more thoughts in our recent interview.… Read More

Bringing EDA to India

Why do all three big EDA companies have user group meetings in India? The answer is to grow the EDA market in India because so many multi-national companies have engineers in India doing SoC, and IP design work. In my 35 years of IC design and EDA experience I’ve had the pleasure of working with and knowing many engineers and managers… Read More

Social Media at Mentor Graphics

You can often tell how important blogging and social media is to an EDA company by how much effort it takes to find their blog from the Home page. For the folks at Mentor Graphics I’d say that blogging is quite important, because it shows up as a top-level menu item. Notice also how important Twitter is, their latest tweets show… Read More

Diagnosing Double Patterning Violations

I’ll bet you’ve read a bunch of stuff about double patterning, and you’re probably hoping that the design tools will make all your double patterning issues just go away. Well, the truth is that the foundries and EDA vendors have worked really hard to make that true.

However, for some critical portions of your design, there … Read More

An easier way to deal with design rule waivers (video)

At advanced nodes, design rules are necessarily more complex and restrictive. Although most of the time you can find a way to live with them, sometimes it’s necessary to seek a waiver from the foundry for a particular design feature. This involves documenting the feature, the design rules in question and the conditions under which… Read More

How to Simplify Complexities in Power Verification?

With multiple functionalities added into a single chip, be it a SoC or an ASIC, maintaining low power consumption has become critical for any design. Various techniques at the technology as well as design level are employed to accomplish the low power target. These include thinner oxides in transistors, different sections of … Read More

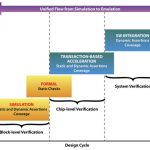

Assertions verifying blocks to systems at Broadcom

Speaking from experience, it is very difficult to get an OEM customer to talk about how they actually use standards and vendor products. A new white paper co-authored by Broadcom lends insight into how a variety of technologies combine in a flow from IP block simulation verification with assertions to complete SoC emulation with… Read More

Mentor Graphics Continues To Perform Well

The EDA tool space has been booming in this new “mobile era” of computing. As the world transitions to system-on-chip design methodologies, and as more teams are developing even more products for an ever-broadening set of end markets, the demand for ever more sophisticated design tools has only continued to skyrocket.… Read More

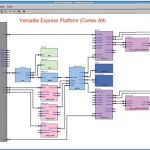

Develop A Complete System Prototype Using Vista VP

Yes, it means complete hardware and software integration, debugging, verification, optimization of performance and power and all other operational aspects of an electronic system in semiconductor design. In modern SoCs, several IPs, RTL blocks, software modules, firmware and so on sit together on a single chip, hence making… Read More