To describe the latest methodology for the addition of Design for Manufacturability fill shapes to design layout data, it’s appropriate to borrow a song title from Bob Dylan – The Times They Are A Changin’. The new technical requirements are best summarized as: “The goal is now to add as much fill as possible, which (ideally) looks… Read More

Something Old, Something New…EDA and Verification

When I got the opportunity to blog about verification, I thought, what new and interesting things should I talk about? Having started my EDA career in 1983, I often feel like one of the “oldies” in this business…remember when a hard drive required a static strap, held a whopping 33 MB, and was the size of a brick? Perhaps they should … Read More

What’s Testing Design Limits at ITC?

The 46[SUP]th[/SUP] IEEE International Test Conference (ITC) will be held the week of October 5, 2015 at the Disneyland Hotel Conference Center in Anaheim, California. ITC is where you will discover the latest ideas and learn about practical applications of test technologies.

As you take in panels, tutorials, presentations,… Read More

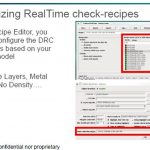

Top 10 Reasons to invest in Interactive Design Rule Checking tools

One of the most energetic presentations at the recent TSMC OIP 2015 symposium was given by Tom Williams from Qualcomm, who shared his insights (and enthusiasm!) for Mentor’s Calibre RealTime interactive Design Rule Checking (iDRC) product.

Paraphrasing Tom’s presentation (and with a tip of the hat to David Letterman), here … Read More

Together At Last—Combining Netlist and Layout Data for Power-Aware Verification

The market demanded that gadgets it loves become ever more conscious of their power consumption, and chip designers responded with an array of clever techniques to cut IC power use. Unsurprisingly, these new techniques added to the complexity of IC verification. When you’re verifying a design that has 100+ separate power domains,… Read More

IoT does NOT lack tools!

Rarely does a month go by without acquisitions in the fabless semiconductor ecosystem. Not surprisingly one of the most read pages on SemiWiki is the EDA Merger and Acquisitions Wiki with more than fifty seven thousand views. It really is a nice family tree, one which we (Daniel Payne) are diligent on keeping current. One of the most… Read More

Moving up Verification to Scenario Driven Methodology

Verification complexity and volume has always been on the rise, taking significant amount of time, human, and compute resources. There are multiple techniques such as simulation, emulation, FPGA prototyping, formal verification, post-silicon testing, and so on which gain prominence in different situations and at different… Read More

Congratulations Dr. Walden C. Rhines!

A funny thing happened at the Design Automation Conference last June in San Francisco. I was browsing the Kaufman award winner mug shots in the EDAC booth and noticed that Wally Rhines was NOT a winner. You can see them HERE. Immediately in disbelief I said to myself: Self, how can this be? Joe Costello, Aart de Geus, and some other guys… Read More

Resolution Enhancement Technology – the key to Moore’s Law

The ability to extend photolithography utilizing 193i light sources to current process nodes is truly the key technical achievement that has enabled Moore’s Law to continue. The interplay between the exposure equipment, the materials – especially, resists and related coatings – and the fundamental principles… Read More

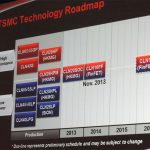

For high-volume manufacturing at 10 nm and below: technology and friendship

The technology for 10 nm is settled, but what about 7 nm and 5 nm? Those nodes will happen with silicon-based CMOS and 193nm immersion lithography, but exactly how is still being worked out. Right now, though, the focus is on getting 10 nm chips into high-volume production. TSMC and Intel both claim to be on track for high-volume manufacturing… Read More