Calibre was a big game changer for DRC users when it first came out. Its hierarchical approach dramatically shortened runtimes with the same accuracy as other existing, but slower, flat tools. However, one unsung part of this story was that getting Calibre up and running required minimal effort for users. Two things are required… Read More

WEBINAR: PAVE360 Validating Autonomous Vehicle Behavior

Siemens Mentor recently announced PAVE360™, a very cool comprehensive pre silicon simulation environment. Autonomous cars are very popular here in Silicon Valley and quite safe on the highways since the average speed is 25mph (horrible traffic). In the city you need autonomous parking unless you want to waste precious time … Read More

Virtualizing 5G Infrastructure Verification

Mentor have pushed the advantages of virtualized verification in a number of domains, initially in verifying advanced networking devices supporting multiple protocols and software-defined networking (SDN), and more recently for SSD controllers, particularly in large storage systems for data centers. There are two important… Read More

Mentor’s Questa verification tools now run on 64-bit ARM based servers

The server market has been undergoing changes in the last few years. The traditional go-to for server processors had been x86 based chips from Intel or AMD. However, if you go on Amazon AWS looking for EC2 instances, you will see the “A1” instance type, which is an ARM based instance. This is not what you might think at first. The A1 instance… Read More

AI Hardware Summit, Report #2: Lowering Power at the Edge with HLS

I previously wrote a blog about a session from Day 1 of the AI Hardware Summit at the Computer History Museum in Mountain View, CA, held just last week. From Day 2, I want to delve into this presentation by Bryan Bowyer, Director of Engineering, Digital Design & Implementation Solutions Division at Mentor, a Siemens Business.… Read More

Virtually Verifying SSD Controllers

Solid State Drives (SSDs) are rapidly gaining popularity for storage in many applications, in gigabytes of storage in lightweight laptops to tens to hundreds of terabyte drives in datacenters. SSDs are intrinsically faster, quieter and lower-power than their hard disk-drive (HDD) equivalents, with roughly similar lifetimes,… Read More

Speeding Up Physical Failure Analysis (PFA)

The cost of an IC depends on many factors like: NRE, masks, fabrication, testing, packaging. Product engineers are tasked with testing each part and understanding what exactly is limiting the yields. Every company has a methodology for Physical Failure Analysis (PFA), and the challenge is to make this process as quick as possible,… Read More

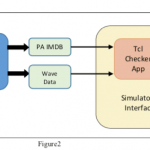

Tcling Your Way to Low Power Verification

OK – maybe that sounds a little weird, but it’s not a bad description of what Mentor suggests in a recent white-paper. There are at least three aspects to power verification – static verification of the UPF and the UPF against the RTL, formal verification of state transition logic, and dynamic verification of at least some critical… Read More

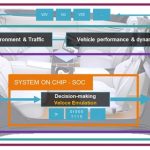

Making pre-Silicon Verification Plausible for Autonomous Vehicles

I love reading about the amazing progress of autonomous vehicles, like when Audi and their A8 model sedan was the first to reach Level 3 autonomy, closely followed by Tesla at Level 2, although Tesla gets way more media attention here in the US. A friend of mine bought his wife a car that offers adaptive cruise control with auto-braking,… Read More

Can a hierarchical Test flow be used on a flat design?

It is pretty common for physical layout to work from a flattened hierarchy for blocks or even full chips, even though the front-end design starts with a hierarchical representation. This was not always the case. Way back when, the physical layout matched the logical hierarchy during the design process. Of course, this led to all… Read More