Last week Mentor hosted a virtual event on designing an AI accelerator with HLS, integrating it together with an Arm Corstone SSE-200 platform and characterizing/optimizing for performance and power. Though in some ways a recap of earlier presentations, there were some added insights in this session, particularly in characterizing… Read More

WEBINAR: Moving UVM Verification Up To The Next Level

Tom Fitzpatrick, a Strategic Verification Architect at Mentor, a Siemens Business, has worked on IEEE and Accellera standards like Verilog 1364, System Verilog 1800, UVM 1800.2 and is Vice Chair of the Portable Stimulus working group, so when I heard that he was doing a webinar on how PSS can be used to create better stimulus for … Read More

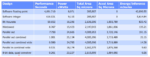

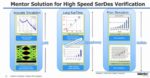

High Speed SerDes Design and Simulation Webinar Replay from Mentor

Over the years SerDes (serializer/deserializer) based connections have proliferated into just about every connection within and among computing systems. Years ago, parallel interfaces were the most common method of moving data, but issues of signal integrity, synchronization and power simply became too much for the required… Read More

DFT Innovations Come from Customer Partnerships

There is an adage that says that quality is not something that can be slapped on at the end of the design or manufacturing process. Ensuring quality requires careful thought throughout development and production. Arguably this adage is more applicable to the topic of Design for Test (DFT) than almost any other area of IC development… Read More

Linux for Medical Devices Q&A

As I have mentioned before SemiWiki gets to meet some very smart people and here is another one. Scot Morrison has an MS degree in Aerospace Engineering from MIT specializing in control systems. Today he is the general manager of the Embedded Platform Solutions Division at Mentor, a Siemens business. Scot oversees the Linux®, Nucleus®,… Read More

Slash Tapeout Times with Calibre in the Cloud

I’ve spent many years in the ASIC business, and I’ve seen my share of complex chip tapeouts. All of these projects share one important challenge – compute requirements explode when you get close to the finish line. Certain tools need to run on the full-chip layout for final verification and the run times for those tools can get excessively… Read More

Radiation Tolerance. Not Just for ISO 26262

Years before ISO 26262 (the auto safety standard) existed, a few electronics engineers had to worry about radiation hardening, but not for cars. Their concerns were the same we have today – radiation-induced single event effects (SEE) and single event upsets (SEU). SEEs are root-cause effects – some form of radiation, might be… Read More

PSS, Test Realization and Reuse

Mentor just released a white paper on this topic which I confess has taxed my abilities to blog the topic. It’s not that the white paper is not worthy – I’m sure it is. I’m less sure that I’m worthy to blog on such a detailed technical paper. But I’m always up for a challenge, so let’s see what I can make of this, extracting a quick and not very… Read More

Mentor Masterclass on ML SoC Design

I was scheduled to attend the Mentor tutorial at DVCon this year. Then coronavirus hit, two big sponsors dropped out and the schedule was shortened to three days. Mentor’s tutorial had to be moved to Wednesday and, as luck would have it, I already had commitments on that day. Mentor kindly sent me the slides and audio from the meeting… Read More

5G SoCs Demand New Verification Approaches

Lately, I’ve been cataloging the number of impossible-to-verify technologies we face. All forms of machine learning and inference applications fall into this category. I’ve yet to see a regression test to prove a chip for an autonomous driving system will do the right thing in all cases. Training data bias is another interesting… Read More