Siemens EDA’s Veloce emulation products are long-established and worthy contenders in any emulation smack-down. But there was always a hole in the complete acceleration story. Where was the FPGA prototyper? Current practice requires emulation for fast simulation with hardware debug, plus prototyping for faster simulation… Read More

Formal for Post-Silicon Bug Hunting? Makes perfect sense

You verified your product design against every scenario your team could imagine. Simulated, emulated, with constrained random to push coverage as high as possible. Maybe you even added virtualized testing against realistic external traffic. You tape out, wait with fingers crossed for first silicon to come back. Plug it into… Read More

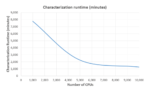

Library Characterization: A Siemens Cloud Solution using AWS

Pressing demands on compute speeds, storage capacity and rapid access to data are not new to the semiconductor industry. A desire for access to on-demand computing resources have always been there. During pre-cloud-computing era, companies provisioned on-demand compute capacity by procuring high performance computing … Read More

Smarter Product Lifecycle Management for Semiconductors

Product Lifecycle Management (PLM) for electronic systems has moved from a passive ‘fire and forget’ approach to one that is intimately involved not only during design, but also throughout the entire life of every unit delivered to the field. Siemens EDA has a white paper titled “Tessent Silicon Lifecycle Solutions” that talks… Read More

Observation Scan Solves ISO 26262 In-System Test Issues

Automotive electronic content has been growing at an accelerating pace, along with a shift from infotainment toward mission critical functions such as traction control, safety systems, engine control, autonomous driving, etc. The ISO 26262 automotive electronics safety standard evolved to help ensure that these systems… Read More

Siemens EDA Wants to Help you Engineer a Smarter Future Faster

In case you missed it earlier this year, Mentor Graphics the oldest EDA brand officially changed its name to Siemens EDA and launched a new website under its parent Siemens Digital Industries Software.

Under Siemens Digital Industries Software, Siemens EDA adds IC, advanced IC packaging and PCB systems design, verification/validation… Read More

Happy Birthday UVM! A Very Grown-Up 10-Year-Old

.The UVM standard was first released by Accellera 10 years ago this month and is now by far the leading methodology for functionally verifying logic designs, especially at the block level. As I write, DVCon fast approaches so I talked to Tom Fitzpatrick, Verification Technologist at Siemens EDA (Mentor Graphics) for a perspective.… Read More

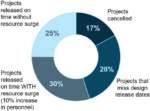

The Five Pillars for Profitable Next Generation Electronic Systems

Although electronic systems design as a discipline has been around ever since electronics systems came into existence (and that was many decades ago), the design complexities involved and the demands and constraints placed on the systems have multiplied significantly since then. Recent research by LifeCycle Insights shows… Read More

Probing UPF Dynamic Objects

UPF was created to go beyond what HDL can do for managing on-chip power. HDLs are agnostic when it comes to dealing with supply & ground connections, power domains, level shifters, retention and other power management related elements of SoCs. UPF fills the breach allowing designers to specify in detail what parts of the design… Read More

Calibre DFM Adds Bidirectional DEF Integration

GDS and LEF/DEF each came about to support data exchange in different types of design flows, custom layout and place & route respectively. GDS (or stream format) was first created in the late 1970s to support the first generation of custom IC layout tools, such as Calma’s GDSII system. Of course, the GDS format has been updated… Read More