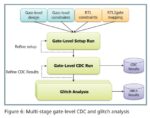

Glitches on clock domain crossing signals have always been a concern for chip designers. Now with increased requirements for reliability, renewed scrutiny is being given to find ways to identify these problems and fix them. In particular applications such as automotive electronics have given this added effort an impetus. Siemens… Read More

RealTime Digital DRC Can Save Time Close to Tapeout

Over the years DRC tools have done an admirable job of keeping pace with the huge growth of IC design size. Yet, DRC runs for sign off on the full design using foundry rule decks take many hours to complete. These long run times are acceptable for final sign off, but there are many situations where DRC results are needed quickly when small… Read More

From Silicon To Systems

The annual Siemens Digital Industries Software user group event was held virtually on May 26th, which made it easy to attend from my home office, although selecting from the list of speakers was a challenge, because they offered 475 sessions, wow. My focus is EDA, so I listened to Joseph Sawicki, the Executive Vice President, IC … Read More

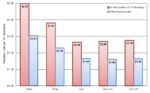

Heterogeneous Chiplets Design and Integration

Over the recent years, the volume and velocity of discussions relating to chiplets have intensified. A major reason for this is the projected market opportunity. According to research firm Omdia, chiplets driven market is expected to be $6B by 2024 from just $645M in 2018. That’s an impressive nine-fold projected increase over… Read More

Siemens EDA Acquires an IP Validation Tool for standard cells, IO and Hard IP

We’re living in an era of good growth for semiconductor design companies, and it’s no secret that each new SoC that comes along contains hundreds of IP blocks, so IP design re-use is just an accepted way of getting to market more quickly with lower risks. But how do we really know that all of the new IP is really correct? … Read More

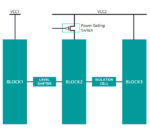

Safety Architecture Verification, ISO 26262

I love to read articles about autonomous vehicles and the eventual goal of reaching level 5, Full Automation, mostly because of the daunting engineering challenges in achieving this feat and all of the technology used in the process. The auto industry already has a defined safety requirements standard called ISO 26262, and one… Read More

Developing Verification Flows for Silicon Photonics

Silicon photonics is getting a lot of interest because it can be used in many applications to improve bandwidth, reduce power and provide novel new functionality. It is especially interesting because it offers an ability to combine electronics and optical elements into the same die. Though it is fabricated with familiar silicon… Read More

Formal Verification Approach Continues to Grow

After a few decades of watching formal verification techniques being applied to SoC designs, it certainly continues to be a growth market for EDA vendors. In the first decades from 1970-1990 the earliest forms of formal tools emerged at technical conferences, typically written by University students earning their Ph.D.s, … Read More

Transistor-Level Static Checking for Better Performance and Reliability

My first transistor-level IC design job was with Intel, doing DRAM designs by shrinking the layout to a smaller process node, and it also required running lots of SPICE runs with manually extracted parasitics to verify that everything was operating OK, meeting the access time specifications and power requirements across PVT … Read More

Embedded Analytics Becoming Essential

SoC integration offers huge benefits through reduced chip count in finished systems, higher performance, improved reliability, etc. A single die can contain billions of transistors, with multiple processors and countless subsystems all working together. The result of this has been rapid growth of semiconductor content … Read More