Who first came up with this term shift-left ? I’d assumed Siemens EDA as they use it so widely. But their latest white paper on the productivity improvements possible with shift-left Calibre IC verification flows puts the record straight: a software engineer called Larry Smith bagged the naming rights in a 2001 paper (leapfrogging… Read More

Emerging Stronger from the Downturn

It was refreshing to hear a talk focused on emerging stronger from the downturn when the news and media are focused on the gloom. At the recent Siemens EDA User2User conference, Joe Sawicki, executive vice president, IC, gave an uplifting keynote talk to the audience. He highlighted a secular growth trend happening in the semiconductor… Read More

Chiplet Modeling and Workflow Standardization Through CDX

Chiplet is a hot topic in the semiconductor world these days. So much so that if one hasn’t heard that term, the person must be living on a very isolated islet. Humor aside, products built using chiplets-based methodology have been in existence for at least some years now. Companies such as Intel, AMD, Apple and others have integrated… Read More

Tessent SSN Enables Significant Test Time Savings for SoC ATPG

SoC test challenges arise due to the complexity and diversity of the functional blocks integrated into the chip. As SoCs become more complex, it becomes increasingly difficult to access all of the functional blocks within the chip for testing. SoCs also can contain billions of transistors, making it extremely time-consuming… Read More

Using ML for Statistical Circuit Verification

I’ve been following Solido as a start-up EDA vendor since 2005, then they were acquired by Siemens in 2017. At the recent User2User event there was a presentation by Kwonchil Kang, of Samsung Electronics on the topic, ML-enabled Statistical Circuit Verification Methodology using Solido. For high reliability circuits… Read More

Achieving Optimal PPA at Placement and Carrying it Through to Signoff

Performance, Power and Area (PPA) metrics are the driving force in the semiconductor market and impact all electronic products that are developed. PPA tradeoff decisions are not engineering decisions, but rather business decisions made by product companies as they decide to enter target end markets. As such, the sooner a company… Read More

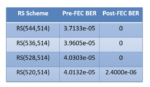

Mitigating the Effects of DFE Error Propagation on High-Speed SerDes Links

As digital transmission speeds increase, designers use various techniques to improve the signal-to-noise ratio at the receiver output. One such technique is the Decision Feedback Equalizer (DFE) scheme, commonly used in high-speed Serializer-Deserializer (SerDes) circuits to mitigate the effects of channel noise and … Read More

Hardware Root of Trust for Automotive Safety

Traveling by car is something that I take for granted and I just expect that my trips will be safe, yet our cars are increasingly using dozens of ECUs, SoCs and millions of lines of software code that combined together present a target for hackers or system failures. The Automotive Safety Integrity Levels (ASIL) are known by the letters:… Read More

Siemens EDA on Managing Verification Complexity

Harry Foster is Chief Scientist in Verification at Siemens EDA and has held roles in the DAC Executive Committee over multiple years. He gave a lunchtime talk at DVCon on the verification complexity topic. He is an accomplished speaker and always has a lot of interesting data to share, especially his takeaways from the Wilson Research… Read More