Functional safety (FuSa) is a big deal, especially when driving a car. My beloved 1998 Acura RL recently exhibited a strange behavior at 239K miles, after making a turn the steering wheel would stay tilted in the direction of the last turn instead of straightening out. The auto mechanic pinpointed the failure to the ball joints, … Read More

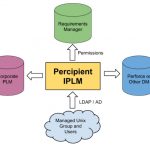

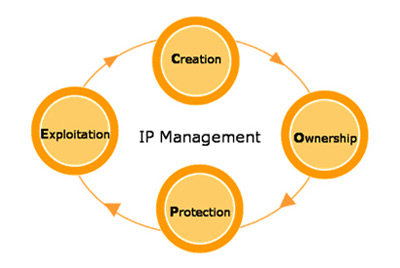

IP Lifecycle Management and Permissions

My first professional experience with computers and file permissions was at Intel in the late 1970s, where we used big iron IBM mainframes located far away in another state, and each user could edit their own files along with browse shared files from co-workers in the same department. I saw this same file permission concept when … Read More

Webinar: ISO 26262 Compliance

To me the major idea of ISO 26262 compliance is ensuring that requirements can be traced throughout the entire design and verification process, including the use of IP blocks. The first market application that comes to mind with ISO 26262 is automotive, with its emphasis on safety because human lives are at stake. Since necessity… Read More

A Brief History of Methodics

Methodics has been a key player in IP management for over 10 years. In this section, Methodics shares their history, technology, and their role in developing IP Lifecycle Management (IPLM) solutions for the electronics industry.

Methodics is recognized as a premier provider of IP Lifecycle Management (IPLM) and traceability… Read More

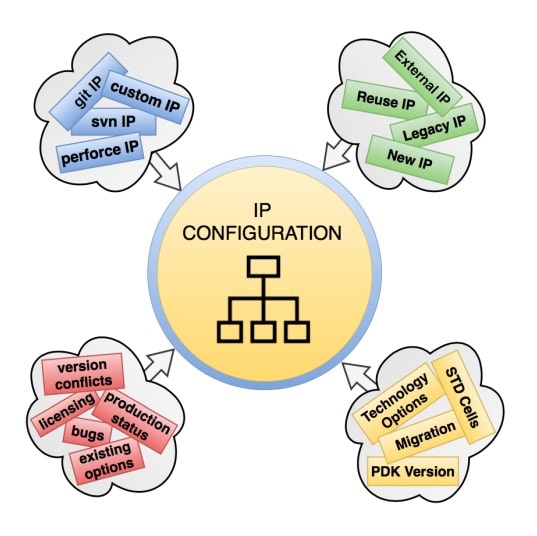

A Brief History of IP Management

As RTL design started to increase in the late 1980’s and early 1990’s, it was becoming apparent that some amount of management was needed to keep track of all the design files and their associated versions. Because of the parallels to software development, design teams looked to the tools and methodologies that were in use by software… Read More

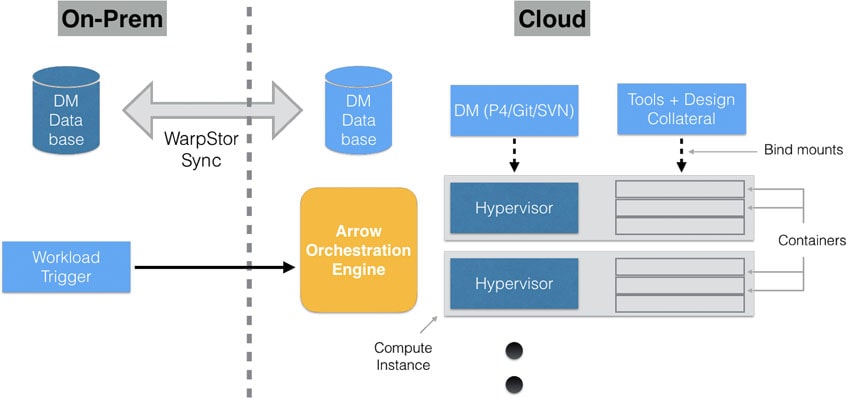

Cloud-based Functional Verification

The big three EDA vendors are constantly putting more of their tools in the cloud in order to speed up the design and verification process for chip designers, but how do engineering teams approach using the cloud for functional verification tests and regressions? At the recent Cadence user group meeting (CDNLive) there was a presentation… Read More

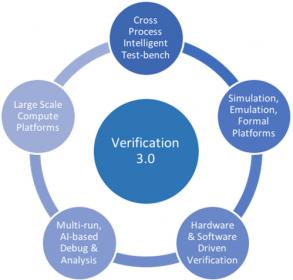

Verification 3.0 Holds it First Innovation Summit

Last week I attended the first Verification 3.0 Innovation Summit held at Levi’s Stadium in Santa Clara along with about 90 other interested engineers and former engineers (meaning marketing and sales people, like me). There was a great vibe and feel to the event as it exuded an energy level that I have not felt at an EDA event in years.… Read More

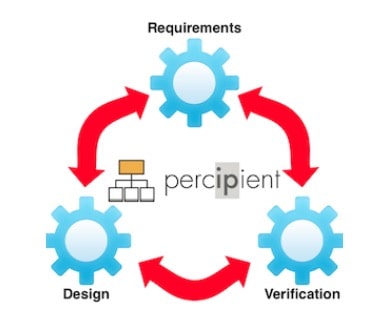

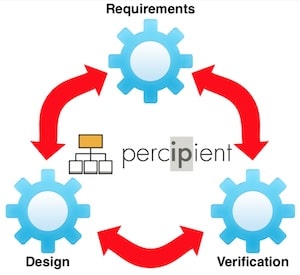

Traceability and Design Verification Synergy

The IC design and verification process can be comprised of many independent point tools, or for more synergy you can have tools that work together by a more synergistic process. We’ve all heard the maxim, “Work smarter, not harder.” A white paper just came out from Methodics on a smarter approach, Traceability… Read More

How Well Did Methodics do in 2018?

In January I read from the ESDA Allianceabout EDA and Semiconductor IP revenues increasing 6.7% for Q3 2018, reaching $2,435.6 million, which is decent growth for our maturing industry. In stark contrast there’s a company called Methodicsthat specializes in Intellectual Property Lifecycle Management (IPLM) and traceability… Read More

SoC Design Partitioning to Save Time and Avoid Mistakes

I started designing ICs in 1978 and continued through 1986, and each chip used hierarchy and partitioning but our methodology was totally ad-hoc, and documented on paper, so it was time consuming to make revisions to the chip or train someone else on the history or our chip, let alone re-use any portion of our chips again. Those old,… Read More