HSPICE users gathered in January 2012 at the HSPICE SIG(Special Interest Group) to talk about their experiences using this circuit simulator for a variety of IC and signal integrity issues. I wasn’t able to attend in person however I did watch the video and wanted to summarize what I heard:… Read More

Electronic Design Automation

Yalta is Dead! Synopsys offensive in VIP restart the cold war

Last year, you could claim (like I did in this blog) that Cadence was making money with large VIP port-folio, when Synopsys was managing sales of a large Design IP port-folio (thanks to a successful acquisition strategy in the 2000’s). But the latest acquisitions made by Synopsys of VIP centric companies like nSys or ExpertIO should… Read More

ISSCC 2012: Silicon Systems for Sustainability!

What can we do for Earth’s sustainability? Besides sorting our garbage and recycling our lawn clippings? Sustainability must be the paramount theme for the future of human society! Semiconductors for a better life! Well, according to my kids, if you take away their smart phones there is no life!… Read More

Synopsys at DVCon: tutorial, lunch, keynote, exhibits and more

DVCon is next week, which I’m sure you know already if you are in verification. Of course Synopsys has a rich product portfolio in verification and verification IP (VIP) so is pretty visible at the show.

On Wednesday they are sponsoring lunch. Several Synopsys customers will talk about their view of how the verification landscape… Read More

Call for Papers: International Gathering for Application Developers!

SemiWiki would like to call you, your co-workers, and your company to participate at ERSA Conference in Las Vegas , July 16-19, 2012. I will be there and it would be a pleasure to work with you on this very important event!

ERSA, is Engineering of Reconfigurable Systems and Algorithms. Since this year, the emphasis will be on the commercial… Read More

Seminar on IC Yield Optimization at DATE on March 14th

My first chip design at Intel was a DRAM and we had a 5% yield problem caused by electromigration issues, yes, you can have EM issues even with 6um NMOS technology. We had lots of questions but precious few answers on how to pinpoint and eliminate the source of yield loss. Fortunately, with the next generation of DRAM quickly introduced… Read More

Custom Processors: Webinar

What is a custom processor? Or Application Specific Instruction-set Processor (ASIP) which is the buzzword which may or may not catch on.

Most programming is done on a processor with a fixed instruction set: think Intel x86 or ARM. Intel or ARM decided on what instructions to include, based on a lot of benchmarking across a wide range… Read More

Pinpoint: Getting Control of Design Data

Back in the Napoleonic era it was possible to manage a battle with very ad hoc methods. Sit on a horse on top of the highest hill and watch the battle unfold, send messengers out with instructions. By the First World War, never mind the second, that approach was hopelessly outdated and a much more structured way of managing a battle was… Read More

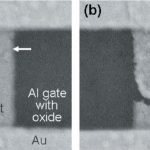

PLL Design Challenges for Integrated Circuit Designs

Nandu Bhagwan is CEO of GHz Circuits and has been designing PLL circuits used in ICs for the past 12 years. Mr. Bhagwan did a video interview with John Pierce of Cadence to talk about the challenges of PLL design.… Read More

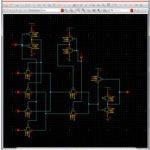

What Changed On My Transistor-Level Schematic?

Digital designers have used diff tools for years on their text-based HDL source code, but what about for the transistor-level IC designer, where is their diff tool for schematics or layout?… Read More

Captain America: Can Elon Musk Save America’s Chip Manufacturing Industry?