You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

WP_Term Object

(

[term_id] => 157

[name] => EDA

[slug] => eda

[term_group] => 0

[term_taxonomy_id] => 157

[taxonomy] => category

[description] => Electronic Design Automation

[parent] => 0

[count] => 4380

[filter] => raw

[cat_ID] => 157

[category_count] => 4380

[category_description] => Electronic Design Automation

[cat_name] => EDA

[category_nicename] => eda

[category_parent] => 0

[is_post] =>

)

RTDA at Alteraby Paul McLellan on 03-12-2013 at 8:05 pmCategories: EDA, FPGA

I talked to Yaron Kretchmer of Altera to find out how they are using RTDA’s products. I believe that Altera are the oldest customer of RTDA, dating back over 15 years, originally used by the operations team around the test floor before propagating out in the EDA and software worlds more recently.

Altera use two RTDA tools, LicenceMonitor… Read More

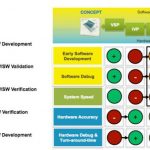

At CDNLive today Frank Schirrmeister presented a nice overview of Cadence’s verification capabilities. The problem with verification is that you can’t have everything you want. What you really want is very fast runtimes, very accurate fidelity to the hardware and everything available very early in the design … Read More

With an HDL-based design methodology many IC engineers code in text languages like SystemVerilog and VHDL, so it’s only natural to use a text-based debug methodology. The expression that, “A picture is worth a thousand words” comes to my mind and in this case a visual debug approach is worth considering for … Read More

You have probably already seen the news: Cadence is acquiring Tensilica for $380M. Cadence has been relatively late to the IP party compared to Synopsys. In contrast, Mentor was early, got into the IP business before it was really profitable and ended up shutting down the business.

Tensilica is quite sizable. It has over 200 licensees,… Read More

At the end of last week I talked to Sanjiv Kaul, the new CEO of Calypto. Just to give a little background for those that haven’t been following along at home, Calypto was founded to try and solve the very hard problem of sequential logical equivalence checking (mostly by people from the engineering team that I managed at Ambit).… Read More

Dr. Paul McLellan and I will be covering CDNLive this week, one of the premier EDA events of the year. Take a look at the agenda and exhibits, this year it looks like a full on Design Automation Conference! There is definitely something for everyone!

Get ready for two full days of content with more than a hundred tracks and keynotes by… Read More

It has be come a cliche to say that “power is the new timing”, the thing that keeps designers up at night and drives the major architectural decisions in big SoCs. Nobody is saying it yet but perhaps “reliability is the new power” will be tomorrow’s received wisdom.

I talked to Adrian Evans of IROCTech… Read More

Tanner EDA is a pleasure to work with, they are big on collaboration and customers absolutely love their tools. With the Synopsys acquisition of SpringSoft, Tanner needs to step up and fill the void of the affordable Laker tools. Take a close look at their new v16 release and let me know how they are doing.

New capabilities for back-end… Read More

We have frequently said in Semiwiki how crucial is it for the SC industry to benefit from high quality PHY IP… even if, from a pure business point of view (MBA minded), PHY IP business does not look so attractive. In fact, to be able to design on-the-edge SerDes and PLL (the two key pieces), you need to build and maintain a highly skilled… Read More

I used my secret powers (being a blogger will get you a press pass) to go to the first day of the SPIE conference on advanced lithography a couple of weeks ago. Everything that happens to with process nodes seems to be driven by lithography, and everything that happens in EDA is driven by semiconductor process. It is the place to find … Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center