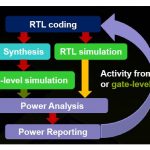

It’s a classic and creative example of design and EDA tool community getting together, exploiting tool capabilities and developing flows which add value to all stake holders including the end consumer. We know power has become extremely important for battery life in smart phones, high performance servers, workstations, notebooks… Read More

Electronic Design Automation

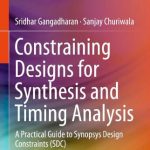

New Book on Design Constraints

There is a new book out from Springer. The subtitle is actually a better description that the title. The subtitle is A Practical Guide to Synopsys Design Constraints (SDC) but the title isConstraining Designs for Synthesis and Timing Analysis. The authors are Sridhar Gangadharan of Atrenta in San Jose and Sanjay Churiwala of Xilinx… Read More

Configurable System IP from a Tool Provider

While I have previously blogged on Forte’s Cynthesizer Workbench’s Interface Generator, I want to take another look from a different perspective. Watching the tool and IP together in action through public videos provided by Forte it struck me as odd what I did not consider earlier, on what should have been obvious to me – Forte is… Read More

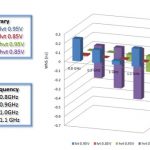

Oasys Bakes a PIE

One challenge in building a modern SoC is that you want to minimize power, performance and area (PPA) while still getting your chip to market on schedule. Realistically, you can’t actually minimize all of these at once since they are tradeoffs: speeding up a critical path often involves upsizing drivers to larger cells which… Read More

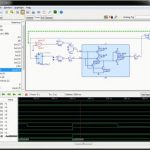

Mixed Signal SOC verification Webinar

When looking at the time to design and verify an SoC we’ve known for many years now that the verification effort requires more time than the design process. So anything that will shorten the verification effort will have the biggest impact on keeping your project on schedule.

A second trend is the amount of Analog content in… Read More

VIA Adopts Cliosoft

VIA Telecom, who makes CDMA base-band processor chips, picked ClioSoft SOS for use by its analog mixed-signal design teams. Like many such teams they use Cadence’s Virtuoso layout platform. ClioSoft’s SOS is seamlessly integrated into Virtuoso so that designers don’t really need to spend much time worrying… Read More

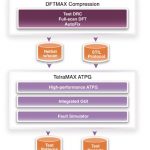

Minimize the Cost of Testing ARM® Processor-based Designs and Other Multicore SoCs

On my first job out of college as an IC design engineer I was surprised to discover that a major cost of chips was in the amount of time spent on the tester before being shipped. That is still true today, so how would you keep your tester time down, test coverage high and with a minimum number of pins when using multiple processors on a single… Read More

Testing an IC Sandwich

At a lovely, but chilly, 3DIncites awards breakfast during SEMICON West, I saw Mentor Graphics win in two of five categories (Calibre 3DSTACK was the other winner). Afterwards, I talked to Steve Pateras, the product marketing director of Mentor’s test solutions about Tessent Memory BIST, which was one of the winners. I asked Pateras… Read More

Aldec Verifies Compatibility of Northwest Logic’s PCI Express Cores with HES-7™ SoC/ASIC Prototyping Platform

Henderson, Nevada – July 11, 2013 –Aldec, Inc., a pioneer in mixed HDL language simulation and hardware-assisted verification solutions, today announced that engineers incorporating high-speed PCI Express data transmission into their SoC and ASIC designs can accelerate their time-to-market utilizing Northwest Logic… Read More

Data Centers accounts for 2 to 3% of WW Energy Consumption!

Do you think this figure will go down? Considering the massive move to Mobile equipment, pushing to de-localize your storage medium to instead use the cloud capabilities, and looking at the huge number of people buying smartphone and tablet in emerging countries, no doubt that Data Center related energy consumption is expected… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center