Synopsys is taking IP-SOC 2013 seriously, as the company will hold several presentations, starting with a Keynote: “Virtual Prototyping – A Reality Check”, by Johannes Stahl, Director, Product Marketing, System-Level Solutions, Synopsys, highlighting current industry practice around putting virtual prototyping to work… Read More

Electronic Design Automation

ARM in Samsung 14nm FinFET

I am at ARM TechCon today. One interesting presentation was made jointly between Samsung, Cadence and ARM themselves about developing physical libraries (ARM), a tool flow (Cadence) and test chips (Samsung). It was titled Samsung ARM and Cadence collaborate on the silicon-proven world first 14-nm FinFET Cortex-A7 ARM CPU and… Read More

ARC EM SEP Processor, Safety Ready Solution for Automotive

If you are familiar with Processor IP core, you certainly know DesignWare ARC EM4 core, 32-bit CPU that SoC designers can optimize for a wide range of uses, and differentiate by using patented configuration technology to tailor each ARC core instance to meet specific performance, power and area requirements. If you develop a product… Read More

Social Media at Mentor Graphics

You can often tell how important blogging and social media is to an EDA company by how much effort it takes to find their blog from the Home page. For the folks at Mentor Graphics I’d say that blogging is quite important, because it shows up as a top-level menu item. Notice also how important Twitter is, their latest tweets show… Read More

Correct by Construction Semiconductor IP

Semiconductor IP re-use enables modern SoC designs to be realized in a timely fashion, yet with hundreds of IP blocks in a chip the chances are higher that an error in any IP block could cause the entire system to fail. At advanced nodes like 28nm and smaller, the number of Process, Voltage and Temperature (PVT) corners is increasing… Read More

MEMS in The World of ICs – How to Quickly Verify?

In the modern electronic world, it’s difficult to imagine any system working as a whole without MEMS (Micro-electromechanical Systems) such as pressure sensors, accelerometers, gyroscopes, microphones etc. working in sync with other ICs. Specifically in AMS (Analog Mixed-Signal) semiconductor designs, there can be significant… Read More

TSMC ♥ Mentor (Calibre PERC)

As semiconductors become more integrated into our lives reliability is becoming a critical issue. As IP consumes more of our die, IP reliability is becoming a critical issue. As we pack more transistors into a chip, reliability is becoming a critical issue. As we move from 28nm to 20nm to 16nm, reliability is becoming a critical … Read More

Diagnosing Double Patterning Violations

I’ll bet you’ve read a bunch of stuff about double patterning, and you’re probably hoping that the design tools will make all your double patterning issues just go away. Well, the truth is that the foundries and EDA vendors have worked really hard to make that true.

However, for some critical portions of your design, there … Read More

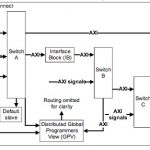

Getting the Most Out of the ARM CoreLink™ NIC-400

SoC designers are attracted to ARM as an IP provider because of their popular offerings and growing ecosystem of EDA partners like Carbon Design Systems. At the upcoming ARM Techcon on October 31 this week in Santa Clara you’ll have an opportunity to hear a joint presentation from ARM and Carbon Design Systems on: Getting … Read More

Cadence’s Mixed-Signal Technology Summit

On October 10, I attended another Cadence Summit, this one titled the Cadence Mixed-Signal Technology Summit. Recently, I had written about the Cadence Silicon Verification Summit. The verification event was the first of its kind, and I thought it had terrific content. Being more of a digital guy myself, I was unaware that Cadence… Read More

The Semiconductor Growth Numbers are Insane but the Real World Doesn’t Tally!