The growing process integration complexity at each technology node has increased development time and cost, and this trend looks to continue. There is a looming risk of delivering unrepeatable critical unit processes (or process modules) that would require revisiting development and manufacturing requalification or in … Read More

Electronic Design Automation

The Pelican Has Landed: Formal on an Unannounced ARM Processor

At the Jasper Users’ Group, Alex Netterville of ARM presented about how ARM are using formal on an unannounced processor code-named Pelican. Don’t read the presentation trying to find out information about Pelican itself, there isn’t any. That wasn’t the topic. Alex has been using formal approaches… Read More

Running Multiple Operating Systems: Hypervisors

How do you run multiple operating systems on the same processor? You use virtualization and you run a hypervisor underneath all the so-called “guest” operating systems. So what is virtualization?

Virtualization started with VM/370 developed in 1972 at IBM (the current version is still in use). Here is how it works.… Read More

Debugging Complex Embedded System – How Easy?

In today’s world of semiconductor design with SoCs having complex IPs, hardware and software working together on a single chip, it’s hard to imagine a system without embedded software into it. But it is easy to guess how difficult it would be to test that hardware and software embedded system. And often there is limited window of … Read More

Data Management in Russia

Milandr is a company based in Moscow that makes high reliability semiconductor components for the aerospace, automotive and consumer markets, primarily in Russia. They work with multiple foundries, including X-FAB and TSMC in technologies from 1um down to 65nm. Corporate headquarter and main IC design house is located in Russian… Read More

Start With The End In Mind – For Complete & Fast Success!

There is always a rush to converge a semiconductor design toward faster closure, amid increasing divergent trends of multiple IPs and high complexities of various functionalities on a single chip. Every design house struggles hard to evolve its customized design flows with several short paths patched up to fix issues, global… Read More

Dassault Patent on Hierarchy Management

Dassault have recently been granted a patent on their approach to managing design hierarchy. I asked them how long it took from filing the patent until it was granted and they said the whole process had taken 8 years. It is a bit of an indictment of the patent system when it takes 8 years, also known as 4 or 5 process nodes, for a patent to… Read More

nVidia: Virtual Platform/Emulation Hybrid

I was the VP marketing at VaST Systems Technology and then at Virtutech. Both companies sold virtual platform technology which consisted of two parts:

- an extremely fast processor emulation technology that actually worked by doing a binary translation of the target binary code (e.g. an ARM) into the native instruction set of the

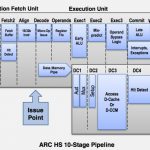

Synopsys Creates a High-performance ARC Core

ARC is a family of configurable processors. Originally it was a standalone company in the UK (what is it with the UK and processor cores?) spun out from Argonaut Software. The A in ARC stood for Argonaut originally. ARC International was acquired by Virage and then Virage was acquired by Synopsys so now it is part of Synopsys Designware… Read More

Addressing Power at Architectural and RTL Levels

Major power reductions are possible by reducing power at the RTL and system levels, and not just at the gate and physical level. In fact, as is so often the case in design, changes can have much more impact when done at the higher level, even given that at that point in the design there is less accurate feedback about changes. Later the… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center