How to handle a new entrant with superior product quality is a point of worried to all EDA companies. Due to continuous research happenings and relatively lower investment requirement new and new EDA start-ups are coming in EDA domains regularly. In several situations, these start-ups offer product of superior quality in terms… Read More

Electronic Design Automation

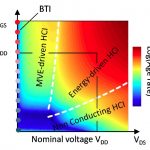

IO Design Optimization Flow for Reliability in 28nm

User group meetings are a rich source of information for IC designers because they have actual designers talking about how they used EDA tools in their methodology to achieve a goal. Engineers at STMicroelectronicspresented at a MunEDAUser Group on the topic: I/O Design Optimization Flow For Reliability In Advanced CMOS Nodes.… Read More

Making IP Reuse and SoC Integration Easier

The last graphics chip that I worked on at Intel was functionally simulated with only a tiny display size of 16×16 pixels, because that size allowed a complete regression test to be simulated overnight. Our team designed three major IP blocks: Display Processor, Graphics Processor and Bus Interface Unit. We wanted to also… Read More

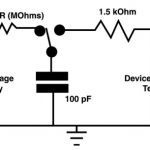

Ensuring ESD Integrity

Electro Static Discharge (ESD) is a fact of life for IC designs and has been ever since electronics were first created and then started failing because of sudden, large currents flowing through the design caused by human, processing or machine contact. It’s just too expensive to layout an IC today, fabricate it, test for … Read More

Then, Python walked in for verification

Go ahead – type “open source” into the SemiWiki search box. Lots of recent articles on the IoT, not so many on EDA tools. Change takes a while. It has only been about five years since the Big Three plus Aldec sat down at the same table to work on UVM. Since then, Aldec has also gotten behind OS-VVM, and is now linked to a relatively new open… Read More

Pizza con Questa

Last week I went to a lunch and learn at Mentor about their Questa formal product given by Kurt Takara. Like everyone else these days, Questa is packaged as a number of Apps for doing different tasks. Formal verification is different from other EDA tools in that different approaches can be used for different sub-tasks. There are three… Read More

How to Trim Automotive Sensor?

The electronic content in automotive is exploding, the market for automotive electronics systems is expected to grow from $170 billion in 2011 to $266 billion by 2016 (Strategy Analytics). When you seat in a brand new car, you immediately see the difference with a ten or even five years old vehicle, as you can exercise MP3 music readers,… Read More

High Tech Headwinds and Project/People Management

In previous posts, we discussed the growing set of challenges and threats faced by the semiconductor industry. From saturating & stagnant systems markets to the gears starting to seize up in that engine of growth we’ve been calling Moore’s Law, chip revenues are – with the exception of memory price boosts from supply… Read More

Enterprise IP Management – A Whole New Gamut in Semiconductor Space

The world of IPs in the semiconductor landscape has completely changed the semiconductor design scenario, specifically the fabless design space. Today IPs are key components of any large semiconductor design, in the same way as auto ancillaries in auto design. It’s just the beginning, in the days to come we will see SoCs just as… Read More

End-to-end look at Synopsys ProtoCompiler

Usually, we get the incremental story in news: this new release is x percent better at this or that than the previous release, and so on. Often missing is the big picture, telling how the pieces all tie together. Synopsys took on that challenge in their latest FPGA-based prototyping webinar. … Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center