You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

WP_Term Object

(

[term_id] => 157

[name] => EDA

[slug] => eda

[term_group] => 0

[term_taxonomy_id] => 157

[taxonomy] => category

[description] => Electronic Design Automation

[parent] => 0

[count] => 4440

[filter] => raw

[cat_ID] => 157

[category_count] => 4440

[category_description] => Electronic Design Automation

[cat_name] => EDA

[category_nicename] => eda

[category_parent] => 0

[is_post] =>

)

Secure Processor for IoTby barun on 02-16-2015 at 1:00 pmCategories: EDA, IoT

In my last blog “Processor for IoT” I have discussed security as one of the key requirements for processor used in IoT devices. In this blog we will analyze different method of hacking and some techniques which can be used to prevent those security breaches.

One of the common ways of attack is to probe address and data … Read More

Lately there has been significant concern over the rising costs of designing in silicon and the troubling decline in venture investments in semiconductors. These alarming trends include fewer IPOs, a falloff in the amount and frequency of early stage seed investments, and comparatively low industry organic growth rates. A … Read More

I got really involved in testability back at CrossCheck in the 1990’s when they designed a way for Gate Arrays to have 100% observability without any Design For Test (DFT) requirements on designers. The Japanese Gate Array companies loved this approach and their customers enjoyed the highest test coverage without being… Read More

Using an assertion is a sure shot method to detect an error at its source, which may be buried deep within a design. It does not depend on a test bench or checker, and can fire automatically as soon as a violation occurs. However, writing assertions manually is very difficult and time consuming. To do so require deep design and coding… Read More

One of the recurring themes I see here in the pages of SemiWiki and elsewhere is this pitched, bordering on religious battle between Altera and Xilinx. Just because both are FPGA technologies, the tendency is to put them in the same bucket, drawing direct comparisons between them. Some folks say there is no comparison; Xilinx has… Read More

Advanced Driving Assistance Systems (ADAS) are an essential element in the vision of autonomous or semi-autonomous vehicles, and they are becoming available today. The ADAS automotive technology raises driving safety by detecting obstacles around the vehicle such as other vehicles and pedestrians, as well as traffic signs… Read More

For about 5 years now Synopsys has held an HSPICE SIG event in conjunction with DesignCon. It features a small vendor faire with companies that partner with Synopsys on HSPICE flows. They also have a dinner with industry/customer speakers and provide an update on HSPICE development. Lastly there is a Q&A where customers get… Read More

As design complexity and size is increasing, SoC verification has become one of the most difficult and time consuming tasks in the design closure.UVM (Universal Verification Methodology, an accellera initiative) is one of the best verification methodologies that support common language, coherent strategy, clarity and transparency… Read More

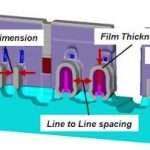

The last paradigm shift in DRC was around 0.35um when designs got too large to handle as flat data, and hierarchical approaches were required. Back then the design rules themselves were not that complex, the explosion of data volume came from the complexity of the design itself. But each process node added more design rules intricacies… Read More

The semiconductor industry has never been more exciting than it is today, at least not in my 30 years of experience. Things are moving faster than ever before making collaboration at all levels a requirement. At SemiWiki we are afforded the privilege of passes to semiconductor conferences around the world. We also have access to… Read More

Silicon Insurance: Why eFPGA is Cheaper Than a Respin — and Why It Matters in the Intel 18A Era