You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

WP_Term Object

(

[term_id] => 157

[name] => EDA

[slug] => eda

[term_group] => 0

[term_taxonomy_id] => 157

[taxonomy] => category

[description] => Electronic Design Automation

[parent] => 0

[count] => 4441

[filter] => raw

[cat_ID] => 157

[category_count] => 4441

[category_description] => Electronic Design Automation

[cat_name] => EDA

[category_nicename] => eda

[category_parent] => 0

[is_post] =>

)

UVM for developing testbenches is a wonderful thing, as most verification engineers will attest. It provides abstraction capabilities, it encapsulates powerful operations, it simplifies and unifies constrained-random testing – it has really revolutionized the way we verify at the block and subsystem level.

However great… Read More

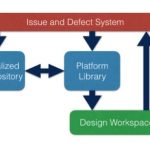

Semiconductor design IP and verification IP have been around for decades, but just because your company has lots of IP doesn’t mean that you’re getting all of the benefits of a design reuse methodology. Maybe your business has encountered some of the following issues:

…

Read More

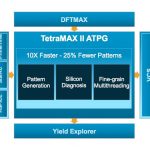

In the life of all EDA software tools comes that moment when new requirements make developers stop and ask, should I continue to refactor the existing code or just start all over from scratch using a new approach? Synopsys came to that junction point when ATPG run times were reaching days or even weeks on the largest IC designs, something… Read More

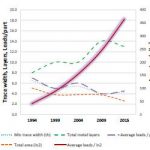

The EDA tool offerings for printed circuit board design commonly address one of three customer markets: (1) the enterprise design team, (2) the product development engineer, and (3) the “maker”. … Read More

After reading previous SemiWiki coverage on Dassault Systèmes and their ENOVIA Pinpoint solution, one big item seemed missing: how does this thing actually work? With all due respect to our other bloggers who covered when Dassault Systèmes acquired Pinpoint from Tuscany Design Automation, why Qualcomm is using Pinpoint, and… Read More

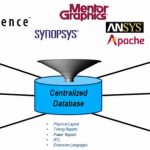

Two weeks ago I spoke on the phone with Albert Li, Founder and CEO of Platform DA about his EDA company. Prior to founding Platform DA in Beijing, Li worked at Accelicon which was acquired by Agilent in December 2011. Mr. Li graduated from Tsinghua University and Vanderbilt University, both in Electrical Engineering, and has written… Read More

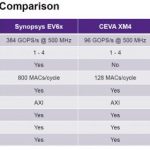

When Synopsys bought Virage Logic in 2010, ARC processor IP was in the basket, but at that time ARC processor core was not the most powerful on the market, and by far. The launch of EV6x vision processor sounds like Synopsys has moved ARC processor core by several orders of magnitude in term of processing power. EV6x deliver up to 100X… Read More

The best things in life may not always be free, but they don’t have to be incredibly difficult to get to. A challenge for IoT designers has been that their bubbling excitement over the potential of their new gizmo is quickly tempered by the complexities of actually building the hardware. Not exactly what they have come to expect in … Read More

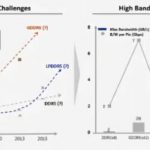

We were waiting to see what a different roster including SK Hynix and Synopsys would have to say on HBM in the latest Open Silicon webinar. This event focused on HBM bandwidth issues; a packaging session on 2.5D interposers was promised for a future webinar.… Read More

Four panelists from big-name semiconductor design companies spoke about their circuit simulation experiences at #53DAC in Austin this year, so I attended to learn more about SPICE and Fast SPICE circuit simulation. I heard from the following four companies:… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center