It is well-known that there is more data being generated all the time. The need to store and process that data with less power and higher throughput dominates design considerations for virtually all systems. There is another dimension to the problem – ensuring the data is secure as all this movement and processing occurs. Within… Read More

Electronic Design Automation

Ansys and eShard Sign Agreement to Deliver Comprehensive Hardware Security Solution for Semiconductor Products

Integrated circuits, or chips, lie at the heart of today’s electronic systems that are mission critical for almost every sector of the economy – from healthcare, to banking, military equipment, cars, planes, telecommunications, and the internet itself. The data flowing through these systems is the lifeblood of modern… Read More

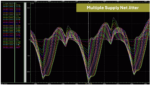

Calibre DesignEnhancer Improves Power Management Faster and Earlier

Anyone who has attempted to implement a custom design in an advanced process node knows that effective power management can be quite challenging. Effects such as voltage (IR) drop and electromigration (EM) can present significant headaches for both design teams and foundries. Optimizing layouts for these kinds of issues is … Read More

Intel and Cadence Collaborate to Advance the All-Important UCIe Standard

The Universal Chiplet Interconnect Express™ (UCIe™) 1.0 specification was announced in early 2022 and a UCIe 1.1 update was released on August 8, 2023. This open standard facilitates the heterogeneous integration of die-to-die link interconnects within the same package. This is a fancy way of saying the standard opens the door… Read More

Keysight EDA and Engineering Lifecycle Management at #61DAC

Entering the exhibit area of DAC on the first floor I was immediately faced with the Keysight EDA booth, and it was even larger than either the Synopsys or Cadence booths. They had a complete schedule of partners presenting in their theatre that included: Microsoft Azure, Riscure, Fermi Labs, BAE Systems, Alphawave, Intel Foundry,… Read More

Bug Hunting in NoCs. Innovation in Verification

Despite NoCs being finely tuned in legacy subsystems, when subsystems are connected in larger designs or even across multi-die structures, differing traffic policies and system-level delays between NoCs can introduce new opportunities for deadlocks, livelocks and other hazards. Paul Cunningham (GM, Verification at Cadence),… Read More

A Closer Look at Conquering Clock Jitter with Infinisim

As voltages go down and frequencies increase, the challenges in chip design become increasingly complex and unforgiving. Issues that once seemed manageable now escalate, while new obstacles emerge, demanding our attention. Among these challenges, clock jitter stands out as a formidable threat. At its core, clock jitter is… Read More

Podcast EP243: What is Yield Management and Why it is Important for Success with Kevin Robinson

Dan is joined by Kevin Robinson, yieldHUB’s Vice President of Operations who was recently appointed Head of Sales for Europe, the Middle East & Africa. With over 23 years of experience as a test engineer in the semiconductor industry, Kevin brings a wealth of knowledge and dedication to his dual role. At yieldHUB, Kevin leads… Read More

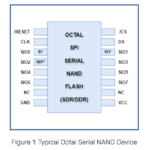

Overcoming Verification Challenges of SPI NAND Flash Octal DDR

As the automotive industry continues to evolve, the demands for high-capacity, high-speed storage solutions are intensifying. Autonomous vehicles and V2X (Vehicle-to-Everything) communication systems generate and process massive amounts of data, necessitating advanced storage technologies capable of meeting these… Read More

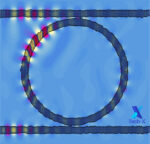

Introducing XSim: Achieving high-quality Photonic IC tape-outs

Similar to analog circuits, which use EM waves at communications frequencies, components in photonics integrated circuits (PICs), which use EM waves at optical frequencies, are sensitive to layout and manufacturing variations—arguably more so. Similar to their semiconductor counterparts, which transmit information… Read More

Should the US Government Invest in Intel?