Portland, Oregon is a hotbed of innovation for software development companies and I tend to scan the headlines of my local newspaper the Oregonian, which is where I first started to read about Jama Software a few years back. Curiosity and opportunity drove me to meet with Trevor Smith of Jama in their Portland office. We chatted for… Read More

Electronic Design Automation

EDA CEO Outlook 2017

A long standing tradition has returned to EDA: The CEO Outlook sponsored by ESDA (formerly EDAC) which alone is worth the price of membership! Not only do you get a free meal, the event included quality networking time with the semiconductor elite. In the past, financial analysts moderated this event holding the CEO’s feet to the… Read More

IoT in the Cloud with Microsoft and Mentor

I cycle for fitness five days per week and use the Strava.com site to post my rides, analyze the ride data and chat with other cyclists, however in February this year the Amazon Web Services went down which crashed Strava, making me sad and nervous at the same time. Of course, there are alternatives to Amazon Web Services and the engineers… Read More

Lip-Bu on Opportunity

Given a chance to talk with someone as connected as Lip-Bu Tan (President and CEO of Cadence and Chairman of the VC firm Walden International), it is tempting to ask all the usual questions about industry growth and directions in cloud, automotive, IIoT, AI and so on. I wanted to try something different. If you make a living (or plan… Read More

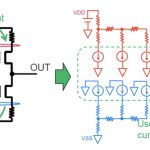

Approaches for EM, IR and Thermal Analysis of ICs

As an engineer I’ve learned how to trade off using various EDA tools based on the accuracy requirements and the time available to complete a project. EDA vendors have been offering software tools to help us with reliability concerns like EM, IR drop and thermal analysis for several years now. Last week I attended a webinar … Read More

A Self-Contained Software-Driven Prototype

You’re building an IP, subsystem or SoC and you want to use a prototype together with a software testbench to drive extensive validation testing. I’m not talking here about the software running on the IP/SoC processor(s); the testbench should wrap around the whole DUT. This is a very common requirement. The standard approach to… Read More

3D Product Design Collaboration in MCAD and ECAD Platforms

Consumer electronics demand aggressive mechanical enclosure design — product volume, weight, shape, and connector access are all critical design optimization criteria. Mechanical CAD (MCAD) software platforms are used by product engineers to develop the enclosure definition — the integration of the PCB design… Read More

The CDNLive Keynotes

I’m developing a taste for user-group meetings. In my (fairly) recently assumed role as a member of the media, I’m only allowed into the keynotes, but from what I have seen, vendors work hard to make these fresh and compelling each year through big-bang product updates and industry/academic leaders talking about their work in bleeding-edge… Read More

Attending DAC in Austin for Free

I’ve been attending DAC since the late 1980’s and can tell you that it’s an annual highlight for me and anyone else interested in the EDA, IP and semiconductor industries. Where else can you see most of the big and little vendors of EDA software, semiconductor IP and foundries in one place? I recently blogged about… Read More

How Far Has Design Automation Brought Us?

It’s always a struggle explaining electronic design automation (EDA) to people who ask me what field I am in. I have come up with simple and minimal descriptions – such as “software used for designing semiconductors.” This, of course, does little to provide any useful understanding to people who are not familiar with the field.… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center