I have seen a flood of verification announcements around directly reading product specs through LLM methods, and from there directly generating test plans and test suite content to drive verification. Conceptually automating this step makes a lot of sense. Carefully interpreting such specs even today is a largely manual task,… Read More

Electronic Design Automation

448G: Ready or not, here it comes!

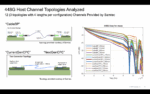

The march toward higher-speed networking continues to be guided by the same core objectives as has always been : increase data rates, lower latency, improve reliability, reduce power consumption, and maintain or extend reach while controlling cost. For the next generation of high-speed interconnects, these requirements … Read More

PDF Solutions and the Value of Fearless Creativity

PDF Solutions has been around for over 30 years. The company began with a focus on chip manufacturing and yield. Since the beginning, PDF Solutions anticipated many shifts in the semiconductor industry and has expanded its impact with enhanced data analytics and AI. Today, the company’s impact is felt from design to manufacturing,… Read More

Moving Beyond RTL at #62DAC

Hardware designers have been using RTL and hardware description languages since the 1980s, yet many attempts at moving beyond RTL have tried to gain a foothold. At the #62DAC event I spent some time with Mike Fingeroff, the Chief High-Level Synthesis Technologist to understand what his company Rise Design Automation is up to. … Read More

Streamlining Functional Verification for Multi-Die and Chiplet Designs

As multi-die and chiplet-based system designs become more prevalent in advanced electronics, much of the focus has been on physical design challenges. However, verification—particularly functional correctness and interoperability of inter-die connections—is just as critical. Interfaces such as UCIe or custom interconnects… Read More

S2C Advances RISC-V Ecosystem, Accelerating Innovation at 2025 Summit China

Shanghai, July 19, 2025 — S2C, a leader in functional verification, showcased its latest digital EDA solutions and key partnerships with BOSC, Xuantie, and Andes Technology at RISC-V Summit China 2025, highlighting its contributions to the ecosystem. The company also played a leading role in the EDA sub-forum, with VP Ying… Read More

Breaking the Sorting Barrier for Directed Single-Source Shortest Paths

Problem & significance.

Single-source shortest paths (SSSP) on directed graphs with non-negative real weights is a pillar of graph algorithms. For decades, the textbook gold standard has been Dijkstra’s algorithm with good heaps, running in the comparison-addition model (only comparisons and additions on weights).… Read More

Chiplets and Cadence at #62DAC

Using chiplets is an emerging trend well-covered at #62DAC and they even had a dedicated Chiplet Pavilion, so I checked out the presentation from Dan Slocombe, Design Engineering Architect in the Compute Solutions Group at Cadence. In a short 20 minutes Dan managed to cover a lot of ground, so this blog will summarize the key points.… Read More

The Critical Role of Pre-Silicon Security Verification with Secure-IC’s Laboryzr™ Platform

As embedded systems and System-on-Chip (SoC) designs grow in complexity and integration, the risk of physical attacks has dramatically increased. Modern day adversaries no longer rely solely on software vulnerabilities; instead, they exploit the physical properties of silicon to gain access to sensitive data. Side-channel… Read More

Podcast EP302: How MathWorks Tools Are Used in Semiconductor and IP Design with Cristian Macario

Dan is joined by Cristian Macario, senior technical professional at MathWorks, where he leads global strategy for the semiconductor segment. With a background in electronics engineering and over 15 years of experience spanning semiconductor design, verification, and strategic marketing, Cristian bridges engineering … Read More

The Semiconductor Growth Numbers are Insane but the Real World Doesn’t Tally!