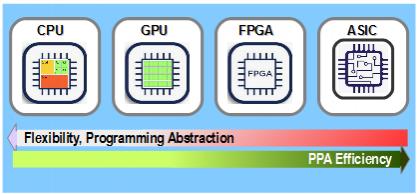

ASIC or FPGA? Each design style has earned designers’ votes depending on the level of urgency, application complexity and funding of their assigned projects. While it is feasible to transition from ASIC to FPGA design or vice versa, such a move is usually done across project refresh instead of midcourse.

Electronic Design Automation

The Latest in Parasitic Netlist Reduction and Visualization

The user group events held by EDA companies offer a unique opportunity to hear from designers and CAD engineers who are actually using the EDA tools “in the trenches”. Some user presentations are pretty straightforward – e.g., providing a quality-of-results (QoR) design comparison when invoking a new tool feature added to a recent… Read More

Portable Stimulus enables new design and verification methodologies

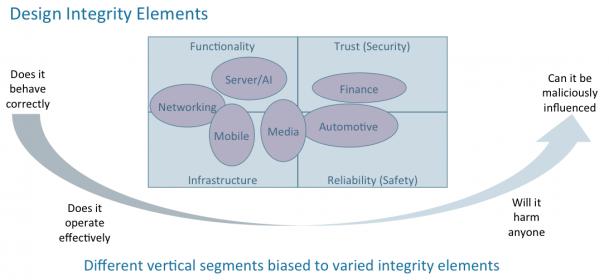

My usual practice when investing is to look at startup companies and try to understand if the market they are looking to serve has a significant opportunity for a new and disruptive technology. This piece compiles the ideas that I used to form an investment thesis in Portable Stimulus. Once collected, I often share ideas to get feedback.… Read More

Advanced Materials and New Architectures for AI Applications

Over the past 50 years in our industry, there have been three invariant principles:

- Moore’s Law drives the pace of Si technology scaling

- system memory utilizes MOS devices (for SRAM and DRAM)

- computation relies upon the “von Neumann” architecture

Technology Behind the Chip

Tom Dillinger and I attended the Silvaco SURGE 2018 event in Silicon Valley last week with several hundred of our semiconductor brethren. Tom has a couple blogs ready to go but first let’s talk about the keynote by Silvaco CEO David Dutton. David isn’t your average EDA CEO, he spent the first 8 years of his career at Intel then spent … Read More

Detail-Route-Centric Physical Implementation for 7nm

For many years TSMC has provided IC design implementation guidance as viewed from the process and manufacturing standpoints. The last time TSMC Reference Flow incremented, it was version 12.0 back in 2011. Since then, increased design, process and packaging related complexities of the advanced nodes have demanded more focused… Read More

Crossfire Baseline Checks for Clean IP Part II

In our previous article bearing the same title, we discussed the recommended baseline checks covering cell and pin presence, back-end, and some front-end checks related to functional equivalency. In this article, we’ll cover the extensive list of characterization checks, that include timing arcs, NLDM, CCS, ECSM/EM, and … Read More

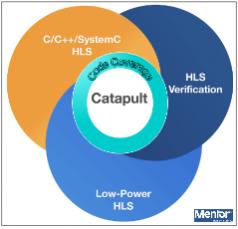

Closing Coverage in HLS

Coverage is a common metric with many manifestation. During the ‘90s, both fault and test coverage were mainstream DFT (Design For Testability) terminologies used to indicate the percentage of a design being observable or tested. Its pervasive use was then spilled over into other design segments such as code coverage, formal… Read More

TSMC and Synopsys are in the Cloud!

EDA has been flirting with the cloud unsuccessfully for many years now and it really comes down to a familiar question: Who can afford to spend billions of dollars on data center security? Which is similar to the question that started the fabless transformation: Who can afford to spend billions of dollars on semiconductor manufacturing… Read More

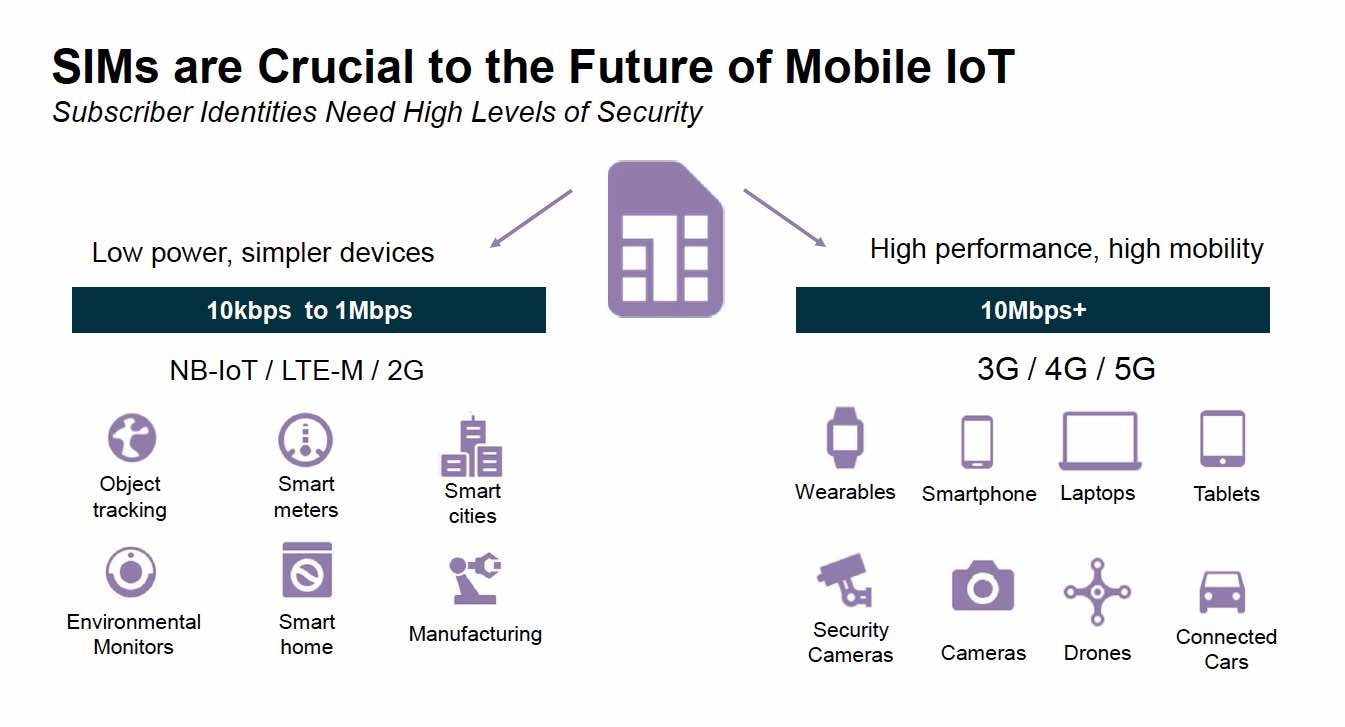

Synopsys Seeds Significant SIM Segue

It turns out that consumers are not alone in their love-hate relationship with SIM cards. SIM cards save us from increasingly widespread cellphone cloning. However, if your experience is anything like mine, it seemed that with every new phone, a new SIM card format was needed. Furthermore, people travelling overseas who wanted… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center