RTLvisionPRO has proven to be an indispensable tool which has greatly improved the productivity and work-flow of our current task: understanding, verifying, and documenting the existing RTL IP library at our company. Consisting of about 500 Verilog and VHDL files, the library has been under development for several years and… Read More

Electronic Design Automation

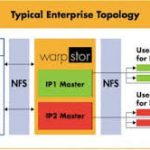

WEBINAR: Lightspeed Data Sync – Design Workspace Problems Solved!

With every process node and every SOC design, engineering and IT teams are experiencing an unprecedented data explosion. User workspaces routinely exceed 10’s of GB and sometimes even 100’s of GB. Regression runs, characterization runs, design and debug of workspaces, building verification environments – all of these… Read More

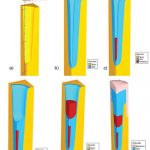

3D TCAD Simulation for Power Devices

My first IC design back in 1978 was a DRAM and it ran on 12V, 5V and -5V, but then my second DRAM was using only a 5V supply. Today we see SOCs running under a 1V supply voltage, but there is a totally different market for power devices that are at the other end of the voltage spectrum and they handle switching ranges from 12V – 250V. … Read More

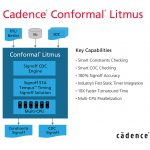

Lint for Implementation

When I was at Atrenta, we took advantage of opportunities to expand our static tool (aka linting) first to clock domain crossing (CDC) analysis and DFT compatibility and later to static analysis of timing constraints, all of which have importance in implementation. CDC is commonly thought of as an RTL-centric analysis, however,… Read More

Tensilica DNA 100 Brings the AI Inference Solution for Level 2 ADAS ECUs and Level 4 Autonomous Driving

I recently wrote about Tensilica’s HiFi DSPs which played a significant role at Cadence’s Automotive Design Summit which was held on the Cadence San Jose campus at the end of July. That article focused on infotainment while briefly touching on Advanced Driver-Assistance Systems (ADAS). ADAS is NOT synonymous with autopilot.… Read More

Build More and Better Tests Faster

Breker has been in the system test synthesis game for 12 years, starting long before there was a PSS standard. Which means they probably have this figured out better than most, quite simply because they’ve seen it all and done it all. Breker is heavily involved in and aligned with the standard of course but it shouldn’t be surprising… Read More

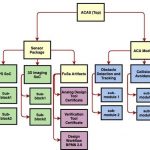

Achieving Functional Safety through a Certified Flow

Functional safety (FuSa) is a big deal, especially when driving a car. My beloved 1998 Acura RL recently exhibited a strange behavior at 239K miles, after making a turn the steering wheel would stay tilted in the direction of the last turn instead of straightening out. The auto mechanic pinpointed the failure to the ball joints, … Read More

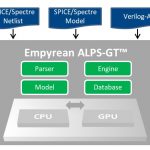

Speeding up Circuit Simulation using a GPU Approach

The old adage that “Time is Money” certainly rings true in the semiconductor world where IC designers are being challenged with getting their new designs to market quickly, and correctly in the first spin of silicon. Circuit designers work at the transistor-level, and circuit simulation is one of the most time-consuming… Read More

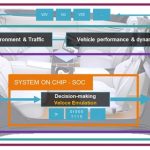

Making pre-Silicon Verification Plausible for Autonomous Vehicles

I love reading about the amazing progress of autonomous vehicles, like when Audi and their A8 model sedan was the first to reach Level 3 autonomy, closely followed by Tesla at Level 2, although Tesla gets way more media attention here in the US. A friend of mine bought his wife a car that offers adaptive cruise control with auto-braking,… Read More

Xilinx on ANSYS Elastic Compute for Timing and EM/IR

I’m a fan of getting customer reality checks on advanced design technologies. This is not so much because vendors put the best possible spin on their product capabilities; of course they do (within reason), as does every other company aiming to stay in business. But application by customers on real designs often shows lower performance,… Read More

Silicon Insurance: Why eFPGA is Cheaper Than a Respin — and Why It Matters in the Intel 18A Era