Ron Lowman, product marketing manager at Synopsys, recently posted an interesting technical bulletin on the Synopsys website entitled How AI in Edge Computing Drives 5G and the IoT. There’s been a lot of discussion recently about the emerging processing hierarchy of edge devices (think cell phone or self-driving car), cloud… Read More

Electronic Design Automation

Webinar on Concurrent Electro-Thermal Analysis for PowerMOS Devices to Improve Performance and Reliability

PowerMOS devices play a major role in a variety of power converter and control circuits. Some examples of their applications include PMICs, or boost and buck converters. Often these are used in mobile and IoT devices to convert battery voltages to circuit operating voltages.

Due to their size and internal complexity PowerMOS … Read More

Bridging the Gap Between Design and Analysis

At the recent DesignCon 2020 in Santa Clara, Cadence introduced a new product, Sigrity Aurora. You won’t find a press release about this announcement. Rather, Brad Griffin, product management group director at Cadence, presented Sigrity Aurora in the theater at the Cadence booth. This one caught my eye and deserves some discussion.… Read More

High-Level Synthesis at the Edge

Custom AI acceleration continues to gather steam. In the cloud, Alibaba has launched its own custom accelerator, following Amazon and Google. Facebook is in the game too and Microsoft has a significant stake in Graphcore. Intel/Mobileye have a strong lock on edge AI in cars and wireless infrastructure builders are adding AI capabilities… Read More

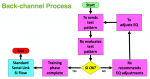

IBIS-AMI Back-Channel System Optimization in Practice

I recently spent some time at DesignCon 2020 in Santa Clara. For those who haven’t attended this show in a while, you need to go. It’s no longer a small event focused on chip design. It has grown into a true system-level conference, with a broad ecosystem represented on the show floor and in the technical sessions. Ecosystem is an important… Read More

Mentor at DVCON 2020!

Are you ready for the premier conference for functional design and verification of electronic systems?

Sponsored by Accellera Systems Initiative, DVCon is an independent, not-for-profit organization dedicated to creating design and verification standards required by systems, semiconductor, intellectual property (IP)… Read More

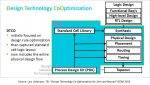

Design Technology CoOptimization at SPIE 2020

SLiC Library tool dramatically accelerates DTCO for 3nm and beyond

In advanced technology nodes below 10nm, Design and Process Technology development have become increasingly intertwined. In older nodes the traditional technology roll-out was done mostly in a sequential manner with clear geometry scaling targets set by … Read More

Thermal Reliability Challenges in Automotive and Data Center Applications – A Xilinx Perspective

I wrote recently on ANSYS and TSMC’s joint work on thermal reliability workflows, as these become much more important in advanced processes and packaging. Xilinx provided their own perspective on thermal reliability analysis for their unquestionably large systems – SoC, memory, SERDES and high-speed I/O – stacked within a … Read More

De-Risking High-Speed RF Designs from Electromagnetic Crosstalk Issue

At DesignCon 2020, ANSYS sponsored a series of very high-quality presentations. Some focused on advanced methods and new technology exploration and some provided head-on, practical and actionable capabilities to improve advanced designs. The presentation I will discuss here falls into the latter category. The topic was… Read More

Innovation in Verification – February 2020

This blog is the next in a series in which Paul Cunningham (GM of the Verification Group at Cadence), Jim Hogan and I pick a paper on a novel idea in verification and debate its strengths and opportunities for improvement.

Our goal is to support and appreciate further innovation in this area. Please let us know what you think and please… Read More

Silicon Insurance: Why eFPGA is Cheaper Than a Respin — and Why It Matters in the Intel 18A Era