I had the opportunity to preview an upcoming webinar on SemiWiki that deals with design robustness for signoff regarding advanced node digital designs (think single-digit nanometers). “Design robustness” is a key term – it refers to high quality, high yielding SoCs that come up quickly and reliably in the target system. We all… Read More

Electronic Design Automation

Six Automated Steps to Design Partitioning for Multi-FPGA Prototyping Boards

Before starting your next FPGA Prototyping Project you should catch the next SemiWiki webinar – “Six Automated Steps to Design Partitioning for Multi-FPGA Prototyping Boards”, in partnership with Aldec.

A significant portion of my 30+ years in the EDA industry has revolved around design verification with some form of FPGA … Read More

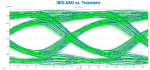

Designing Next Generation Memory Interfaces: Modeling, Analysis, and Tips

At DesignCon 2020, there was a presentation by Micron, Socionext and Cadence that discussed design challenges and strategies for using the new low-power DDR specification (LPDDR5). As is the case with many presentations at DesignCon, ecosystem collaboration was emphasized. Justin Butterfield (senior engineer at Micron)… Read More

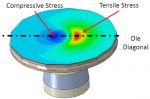

Reliability Challenges in Advanced Packages and Boards

Today’s Market Requirements

Complex electronic devices and (sub)systems work for us in important applications, such as aircrafts, trains, trucks, passenger vehicles as well as building infrastructure, manufacturing equipment, medical systems and more. Very high reliability (the ability of a product to meet all requirements… Read More

An Important Step in Tackling the Debug Monster

If you’ve spent any time at all in the semiconductor industry, you’ve heard the statement that verification consumes two-thirds or more of the total resources on a chip project. The estimates range up to 80%, in which case verification is taking four times the effort of the design process. The exact ratio is subject to debate, but… Read More

Navigating Memory Choices for Your Next Low-Power Design

Choosing a memory architecture can be a daunting task. There are many options to choose from, each with their own power, performance, area and cost profile. The right choice can make a new design competitive and popular in the market. The wrong choice can doom the whole project to failure.

Vadhiraj Sankaranarayanan, senior technical… Read More

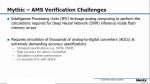

Mentor Helps Mythic Implement Analog Approach to AI

The entire field of Artificial Intelligence (AI) has resulted from what is called “first principles thinking”, where problems are re-examined using a complete reassessment of the underlying issues and potential solutions. It is a testament to how effective this can be that AI is being used for a rapidly expanding number of applications… Read More

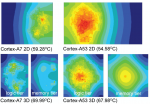

Thermal Issues and Solutions for 3D ICs: Latest Updates and Future Prospect

At DesignCon 2020, ANSYS held a series of sponsored presentations. I was able to attend a couple of them. These were excellent events with the material delivered by talented and high-energy speakers. The DesignCon technical program has many dimensions beyond the conference tracks. One of the presentations dealt with 3D ICs.… Read More

Hybrid Verification for Deep Sequential Convergence

I’m always curious to learn what might be new in clock domain crossing (CDC) verification, having dabbled in this area in my past. It’s an arcane but important field, the sort of thing that if missed can put you out of business, but otherwise only a limited number of people want to think about it to any depth.

The core issue is something… Read More

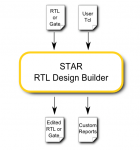

Build Custom SoC Assembly Platforms

I’ve talked with Defacto on and off for several years – Chouki Aktouf (CEO) and Bastien Gratreaux (Marketing). I was in a similar line of business back in Atrenta. Now I’m just enjoying myself, I’ve written a few blogs for them. I’ll confess I wondered why they wouldn’t struggle with the same problems we’d had. Script-driven RTL editing,… Read More

Silicon Insurance: Why eFPGA is Cheaper Than a Respin — and Why It Matters in the Intel 18A Era