For 5G to really deliver on its promise of high bandwidth and good coverage, it needs to use an RF band known as C-Band (3.7 to 4.4 GHz). This band is ideal because its frequency is high enough to offer 100MHz wide channels and also low enough that signal attenuation, especially in urban areas, is minimal. In 2020 the FCC auctioned off… Read More

Electronic Design Automation

Six Essential Steps For Optimizing EDA Productivity

Altair® Accelerator™ was the focus of a couple of SemiWiki posts last year. The most recent post covers the enterprise-grade job scheduler’s latest updates and an earlier one discussed its patented Rapid Scaling feature. You can refer to these blogs here. While these posts provide insight into how Accelerator can help increase… Read More

Automated Documentation of Space-Borne FPGA Designs

Over the past three years, I’ve spoken frequently with Cristian Amitroaie, CEO and co-founder of AMIQ EDA, to understand how the company is helping engineers cope with the challenges of chip design and verification. With their broad customer base and many years of experience in the EDA business, the folks at AMIQ really seem to … Read More

Dynamic Coherence Verification. Innovation in Verification

We know about formal methods for cache coherence state machines. What sorts of tests are possible using dynamic coherence verification? Paul Cunningham (GM, Verification at Cadence), Raúl Camposano (Silicon Catalyst, entrepreneur, former Synopsys CTO) and I continue our series on research ideas. As always, feedback welcome.… Read More

Verific Sharpening the Saw

Verific is an unusual company. They are completely dominant in what they do – providing parsers for Verilog/SV, VHDL and UPF. Yet they have no ambition to expand beyond that goal. Instead, per Michiel Ligthart (President and COO), they continue to “sharpen the saw”. This is an expression I learned in sales training, habit #7 from… Read More

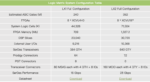

S2C’s FPGA Prototyping Solutions

Prototyping solutions have been in the news a lot lately. And FPGA-based prototyping approach is pretty widely used. On a panel session at DAC 2021, Amir Salek, Head of Silicon for Cloud and Infrastructure at Google had the following to say. Prototyping FPGA is a tremendous platform for testing and validation. We are doubling down… Read More

Agile SoC Design: How to Achieve a Practical Workflow

“The only sustainable advantage you can have over others is agility, that’s it.” (Jeff Bezos)

The best workflow is the one that has been working until it doesn’t. In their quest to tape-out the next design, SoC teams rely on their proven workflow to meet design constraints and project milestones. As often the case, design … Read More

Future of Semiconductor Design: 2022 Predictions and Trends

Predictions and trends create the forces that accelerate innovations and keep the industry moving forward. We are all used to hearing of important issues and challenges, usually in the context of solutions offered by various vendors. The SemiWiki forum plays its role in bringing awareness of all of the above to its audience. For… Read More

The Semiconductor Ecosystem Explained

The last year has seen a ton written about the semiconductor industry: chip shortages, the CHIPS Act, our dependence on Taiwan and TSMC, China, etc.

But despite all this talk about chips and semiconductors, few understand how the industry is structured. I’ve found the best way to understand something complicated is to diagram… Read More

Why It’s Critical to Design in Security Early to Protect Automotive Systems from Hackers

Remember when a pair of ethical hackers remotely took over a Jeep Cherokee as it was being driven on a highway near downtown St. Louis back in 2015? The back story is, those “hackers,” security researchers Charlie Miller and Chris Valasek, approached vehicle manufacturers several years before their high-profile feat, warning… Read More

Silicon Insurance: Why eFPGA is Cheaper Than a Respin — and Why It Matters in the Intel 18A Era