I was born in the UK (then still a part of Europe), so always eager to see them succeed. But I must admit that past behavior has reinforced the view that the EU’s only active “contribution” to progress is regulation. However this seems to be changing in multiple interesting ways. On a grand scale, the Nordic economic model is taking … Read More

Electronic Design Automation

Siemens EDA Expands AI and Advanced Packaging Collaboration with TSMC

At the recent TSMC Technology Symposium 2026, Siemens EDA reinforced its position as one of the key ecosystem partners supporting TSMC in the race toward AI-driven semiconductor design, advanced packaging, and next-generation process technologies. The annual forum has become one of the semiconductor industry’s most important… Read More

CEO Interview with Nagesh Gupta of llmda.ai

Nagesh has built a career spanning multiple aspects of system design and development at companies including Hewlett-Packard, Cadence, Xilinx, and Lattice Semiconductor.

He is also a serial entrepreneur. Nagesh founded Taray, Inc., which developed memory interface generators for Xilinx designs and was later acquired by … Read More

The “New Shift-Left”: Why FPGA Prototyping is the Ultimate RISC-V IP Sandbox

In the EDA world, “Shift-Left” has traditionally been a mantra for early software development—booting the OS before the silicon even leaves the fab. But as the RISC-V revolution accelerates, the goalposts have moved. We are seeing the emergence of a “New Shift-Left”, one that focuses on critical architectural… Read More

Beyond Tool Interoperability: The Emerging Governed Convergence Problem in Semiconductor Design

The semiconductor industry has spent decades optimizing tools. Today, however, the central challenge is no longer whether individual tools are powerful enough. The real question is whether increasingly specialized tools, domains, models, and organizations can still converge coherently into a manufacturable, reliable,… Read More

IPLM: Future Forward Webinar May 19th

Step into the future of semiconductor design management with IPLM: Future Forward, a product-led webinar showcasing the latest developments in Perforce IPLM. This focused session is designed to show how modern teams can tackle growing design complexity while still accelerating innovation.

Hosted by IPLM… Read More

From Point Solutions to Agentic AI Ecosystems: Semiconductor Process Control Depends on Its Past

Agentic AI is often presented as a revolutionary shift in semiconductor manufacturing, driven by large language models and generative AI. However, this framing overlooks an important reality: today’s advances are built on decades of prior work. As Jonathan Holt of PDF Solutions emphasizes in his recent keynote at the APCM 2026… Read More

CEO Interview with Dave Kelf, CEO of Breker Verification Systems

In the functional verification space, Breker Verification Systems stands out for its vast and long-standing understanding and ability to solve many of the seemingly intractable complexity challenges, especially in the system space.

I recently talked with Dave Kelf, Breker’s CEO, who has plenty of good news to share about Breker’s… Read More

The Great Divide: A Tale of Three Hardware Emulation Architectures

Hardware emulation arose as a necessity out of the needs of the eighties. By the mid-1980s, semiconductor designs had outgrown the practical limits of gate-level simulation. Gate-level simulation delivered accuracy, but at glacial pace; silicon prototypes performed at real-speed but arrived far too late. The industry needed… Read More

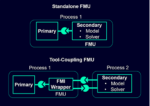

A Different Angle on Co-Simulation for Systems

Co-simulation, two or more simulations running concurrently in some manner, is not a new idea. I have written before about multiphysics systems able to model thermal, stress, CFD and other factors simultaneously. I just read a white paper from Siemens based on a different method, using an open standard called the Functional Mockup… Read More

From the Selfie to Samantha: The Next Trillion-Dollar Behavior