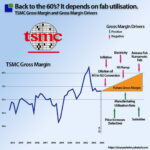

If you work in the Semiconductor or related industry, you know that industry cycles can profoundly impact your business. It is crucial for strategic development to invest at the appropriate time and to rope the sails when necessary.

As a semiconductor investor, you’re accustomed to the ebb and flow of industry cycles. It’s… Read More

From the Selfie to Samantha: The Next Trillion-Dollar Behavior