At the recent RISC-V Now event hosted by Andes, the discussion underscored the fact that RISC-V is no longer just about instruction set architecture advantages or customizable cores. The real focus has moved up the stack to system-level design. This is where connectivity, integration, and security define whether an innovation… Read More

Scalable Network-on-Chip Enables a Modular Chiplet Platform

The semiconductor industry is undergoing a profound transformation as system complexity, performance expectations, and time-to-market pressures continue to rise. Traditional monolithic system-on-chip (SoC) designs are increasingly giving way to modular, chiplet-based architectures that enable flexibility, scalability,… Read More

Renesas Scalable Automotive SoC Design Using Arteris NoC

The increasing complexity of advanced driver assistance systems (ADAS) and automated driving architectures has driven a transition from traditional bus-based interconnects to scalable Network-on-Chip (NoC) fabrics. Renesas’ next-generation R-Car automotive SoC platforms adopt Arteris FlexNoC interconnect intellectual… Read More

NXP Expands Arteris NoC Deployment to Scale Edge AI Architectures

As edge AI systems become more centralized and compute-dense, on-chip data movement is increasingly the architectural bottleneck. NXP’s expanded deployment of Arteris network-on-chip (NoC) and cache-coherent interconnect IP highlights a broader industry trend: interconnect architecture is now a first-order design … Read More

Arteris Highlights a Path to Scalable Multi-Die Systems at the Chiplet Summit

At the recent Chiplet Summit, presentations, discussions and general participation could be broken down into a few broad categories. There were presentations of actual chiplet designs, either as building blocks or end products. There were presentations regarding design tools and methodologies to support and accelerate … Read More

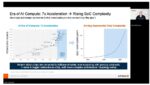

The Next Hurdle AI Systems Must Clear

AI isn’t having an easy ride. The media and Wall Street swing wildly between extremes on any hint of a shift in AI sentiment. Dickens saw this coming: “It was the best of times, it was the worst of times, it was the age of wisdom, it was the age of foolishness, it was the epoch of belief, it was the epoch of incredulity, it was the season of … Read More

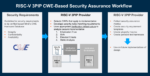

Securing RISC-V Third-Party IP: Enabling Comprehensive CWE-Based Assurance Across the Design Supply Chain

by Jagadish Nayak

RISC-V adoption continues to accelerate across commercial and government microelectronics programs. Whether open-source or commercially licensed, most RISC-V processor cores are integrated as third-party IP (3PIP), potentially introducing supply chain security challenges that demand structured,… Read More

Arteris Smart NoC Automation: Accelerating AI-Ready SoC Design in the Era of Chiplets

As semiconductor design pushes into increasingly complex territory, driven by Ai, ML, HPC, and heterogeneous system architectures, designers are challenged to balance performance, power, and time-to-market pressures. In this landscape, network-on-chip (NoC) architectures have emerged as a foundational building block… Read More

WEBINAR: Why Network-on-Chip (NoC) Has Become the Cornerstone of AI-Optimized SoCs

By Andy Nightingale, VP of Product Management and Marketing

As AI adoption accelerates across markets, including automotive ADAS, large-scale compute, multimedia, and edge intelligence, the foundations of system-on-chip (SoC) designs are being pushed harder than ever. Modern AI engines generate tightly coordinated, … Read More

Live Webinar: Considerations When Architecting Your Next SoC: NoC with Arteris and Aion Silicon

The explosive growth of AI and accelerated computing is placing unprecedented demands on system-on-chip (SoC) design. Modern AI workloads require extremely high bandwidth, ultra-low latency, and energy-efficient data movement across increasingly heterogeneous architectures. As SoCs scale to incorporate clusters of… Read More