You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

A response to Daniel Nenni’s “What’s Wrong with Intel?” article, which invited alternative views.

At the risk of calling down the forecast universal opprobrium, I’m going to disagree with Dan’s take on the centrality of Intel.

I don’t agree that Intel is too big/important to fail or that the US can’t succeed in semiconductors without… Read More

Advanced process nodes create challenges for EDA both in handling ever larger designs and increasing design process complexity.

Shift-left design methodologies for design cycle time compression are one response to this. And this has also forced some rethinking about how to build and optimize design tools and flows.

SemiWiki… Read More

Siemens EDA’s next move in its Calibre shift left strategy is the addition of correct-by-construction IC layout optimization for the most critical emerging physical design challenges. Calibre’s new DesignEnhancer product supports both custom and digital ICs and is already in use by several leading IC design companies. It … Read More

Who first came up with this term shift-left ? I’d assumed Siemens EDA as they use it so widely. But their latest white paper on the productivity improvements possible with shift-left Calibre IC verification flows puts the record straight: a software engineer called Larry Smith bagged the naming rights in a 2001 paper (leapfrogging… Read More

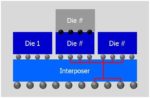

If, like me, you’ve been paying too little attention to historically less glamorous areas of chip design like packaging, you’ll wake up one day and realize just how much things have changed and continue to advance and how interesting it’s become.

One of the main drivers here is the increasing use of chiplets to counter the decreasing… Read More

You don’t often hear about the inner workings of EDA tools and flows – the marketing guys much prefer telling us about all the exciting things their tools can do rather than the internal plumbing. But this matters for making design flows – and building these has largely been left to the users to sort out. That’s an increasing challenge… Read More

SemiWiki readers from a digital IC background might find it surprising that post-PCB route analysis for high speed serial links isn’t a routine and fully automated part of the board design process. For us, the difference between pre- and post-route verification is running a slightly more accurate extraction and adding SI modelling,… Read More

The last thing you want when taping out a design is to hit large numbers of violations in signoff checks that could have been flushed out and resolved in earlier flow iterations. For implementation flows (floorplanning, synthesis, place and route), it’s usual to do a lot of flow flushing work early in the design cycle and iteratively… Read More

Chemical Origins of Environmental Modifications to MOR Lithographic Chemistry