GDS and LEF/DEF each came about to support data exchange in different types of design flows, custom layout and place & route respectively. GDS (or stream format) was first created in the late 1970s to support the first generation of custom IC layout tools, such as Calma’s GDSII system. Of course, the GDS format has been updated… Read More

Author: Tom Simon

Calibre DFM Adds Bidirectional DEF Integration

Automotive SoCs Need Reset Domain Crossing Checks

When the number of clock domain crossings (CDCs) in SoCs proliferated it readily became apparent that traditional verification methods were not well suited to ensuring that they were properly handled in the design. This led to the creation of new methods and tools to check for correct interfaces between domains. Now, in automotive… Read More

Achronix Speedster7t Garners Best Practices Award for FPGA

FPGAs have played an important role in the growth of key markets, including networking, storage, mobile devices, etc. They offer a unique set of capabilities that ASICs, CPUs and GPUs find hard to match. FPGAs are wire-speed, programmable integrated circuits that accelerate data and applications. The ability to reprogram … Read More

Sensor Fusion Brings Earbuds into the Modern Age

Ten years ago, earbuds might have seemed like a mundane product area with little room for exciting developments. Truly Wireless Stereo (TWS) has coincided with an avalanche of innovations that have moved earbuds from a simple transducer for creating sound into being a sophisticated device capable of accepting user commands … Read More

Achronix Talks about FPGAs for Video Processing

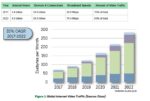

The internet keeps adding users and connected devices. According to the numbers in a white paper from Achronix, by 2022 there will be 4.8 billion internet users and 28.5 billion connected devices. Internet traffic will reach 275 exabytes per month. Of this a staggering 83 percent will be video traffic. Moving the data from creators… Read More

Configuration Environment is Make-or-Break for IC Verification

All semiconductor design work today rests on the three-legged stool of Foundries, EDA Tools and Designers. Close collaboration between the three make possible the successful completion of ever more complex designs, especially those at advanced nodes. Perhaps one of the most critical intersections of all three is during physical… Read More

Verification IP proves essential for PCIe GEN5

PCI Express (PCIe) has become an important communication element in a wide range of systems. It is used to connect networking, storage, FPGA and GPGPU boards to servers and desktop systems. It has progressed a long way from its initial parallel bus format. Its evolution to a serial point to point configuration has been accompanied… Read More

Sign Off Design Challenges at Cutting Edge Technologies

As semiconductor designs for many popular products move into smaller process nodes, the need for effective and rapid design closure is increasing. The SOCs used for many consumer and industrial applications are moving to FinFET nodes from 16 to 7nm and with that comes greater challenges in obtaining design closure. einfochips,… Read More

Low Power SRAM Register Files for IoT, AI and Wearables

SRAM is the workhorse for on-chip memories, valued for its performance and easy integration with standard processes. The needs of wearable, IoT and AI SOCs have put a lot of pressure on the requirements for all on-chip memories. This is perhaps most evident in the area of power. AI chips that rely heavily on SRAM register files are… Read More

Webinar Replay on TileLink from Truechip

The extremely popular RISC-V instruction set architecture (ISA) originally came from the Berkeley Architecture Research (BAR) group. BAR also developed several other key pieces of enabling technology that have helped RISC-V become so popular. Among these are Rocket Chip which serves as a RISC-V based SOC generator. It can … Read More

Tesla and Samsung Relationship Update