The ability to extend photolithography utilizing 193i light sources to current process nodes is truly the key technical achievement that has enabled Moore’s Law to continue. The interplay between the exposure equipment, the materials – especially, resists and related coatings – and the fundamental principles… Read More

Author: Tom Dillinger

Introduction to FinFET Technology Part III

The preceding two Semiwiki articles in this thread provided an overview to the FinFET structure and fabrication. The next three articles will discuss some of the unique modeling requirements and design constraints that FinFET’s introduce, compared to planar FET technology.

Due to the complexity of FinFET modeling – … Read More

Intel’s finfets too complex and difficult?

Thanks to SemiWiki readers for the feedback and comments on the previous “Introduction to FinFET Technology” posts – very much appreciated! The next installment on FinFET modeling will be uploaded soon.

In the interim, Dan forwarded the following link to me “ Intel’s FinFETs too complicated and difficult, says … Read More

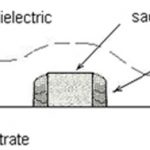

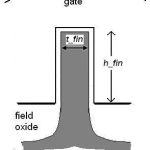

Introduction to FinFET technology Part II

The previous post in this series provided an overview of FinFET devices. This article will briefly cover FinFET fabrication.

The major process steps in fabricating silicon fins are shown in Figures 1 through 3. The step that defines the fin thickness uses Sidewall Image Transfer (SIT). Low-pressure chemical vapor (isotropic)… Read More

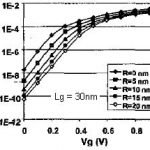

Introduction to FinFET technology Part I

This is the first of a multi-part series, to introduce FinFET technology to SemiWiki readers. These articles will highlight the technology’s key characteristics, and describe some of the advantages, disadvantages, and challenges associated with this transition. Topics in this series will include FinFET fabrication,… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center