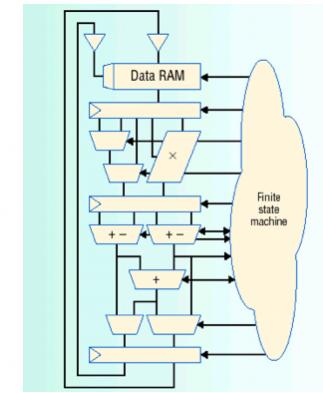

Almost any chip of any complexity contains a control processor of some sort. These blocks are good at executing a wide range of algorithms but there are often two problems with them: the performance is inadequate for some application or the amount of power required is much too high. Control processors pay in limited performance … Read More

Author: Paul McLellan

RTL Power Models

One of the challenges of doing a design in the 28nm world is that everything depends on everything else. But some decisions need to be made early with imperfect information. But the better the information we have, the better those early decisions will be. One area of particular importance is selecting a package, designing a power… Read More

Think differentiation

Wally Rhines’s keynote at the ARM TechCon was about differentiation and how to use it to create measurable value. We all know what differentiation means in some intuitive sense, but how do you make it measurable? Wally’s answer was that differentiation is a measure of the difficulty of switching suppliers and is best… Read More

Synopsys Journal, now on Itunes

Synopsys Journal is a quarterly publication for management dedicated to covering the latest issues facing designers today. It has been published now for two and a half years. Of course, you can go here and, once registered, get a copy of the journal.

But people don’t have a lot of time to read a journal like this so it has been … Read More

Noise Coupling

One of the challenges of designing a modern SoC is that the digital parts of the circuit are really something that in an ideal world you’d keep as far away from the analog as possible. The digital parts of the circuit generate large amounts of noise, especially in the power supply and in the substrate, two areas where it is impossible… Read More

Apache on the Road

There are lots of places that Apache is going to popping up in the next few weeks.

Firstly, Andrew Yang will deliver the keynote on October 24th at the Electrical Performance of Electronic Packaging and Systems (EPEPS) in San Jose. He will be talking about “Chip-Package-System convergence: bridging multiple disciplings… Read More

Austin and San Jose SCC

Don’t forget the SpringSoft Community Conferences next week in Austin on Tuesday and in San Jose on Thursday. There is no charge and you even get a free lunch (see “no such thing as…”).

The morning in Austin is focused on functional closure and how to leverage SpringSoft’s verification technology… Read More

Soft IP Qualification

At the TSMC Open Innovation Platform Ecosystem Forum (try saying that three times in a row) next week (on Tuesday 18th), Atrenta will present a paper on the TSMC soft IP qualification flow. It will be presented by Anuj Kumar, senior manager of the customer consulting group.

More and more, chips are not put together what we think of … Read More

Jasper User Group Meeting

Jasper’s Annual User Group Meeting is on November 9th and 10th, in Cupertino California. It will feature users from all over the world sharing the best practices in verification. If you are a user of Jasper’s products then you should definitely plan to attend. This year there is so much good material that the meeting… Read More

SoC Realization: Let’s Get Physical!

If you ask design groups what the biggest challenges are to getting a chip out on time, then the top two are usually verification, and getting closure after physical design. Not just timing closure, but power and area. One of the big drivers of this is predicting and avoiding excessive routing congestion, which is something that … Read More

Silicon Insurance: Why eFPGA is Cheaper Than a Respin — and Why It Matters in the Intel 18A Era