You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

Prolog – Interface Protocols: Achilles’ Heels in Today’s State-of-the-art SOCs

June 30 was only a week away when Varun had a sleepless night. The call from the datacenter manager the evening before alerted him on a potential problem with the training of a new Generative AI model. Six months earlier Varun’s employer installed… Read More

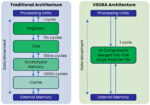

VSORA AI Processor Raises $46 Million to Fast-Track Silicon Development

We stand on the cusp of an era defined by ubiquitous intelligence—a stone’s throw from a tidal wave of AI-powered products underpinned by next-generation silicon. Realizing that future demands nothing less than a fundamental rethink of how we design semiconductors… Read More

At this year’s SNUG (Synopsys Users Group) conference, Richard Ho, Head of Hardware, OpenAI, delivered the second keynote, titled “Scaling Compute for the Age of Intelligence.” In his presentation, Richard guided the audience through the transformative trends and implications of the intelligence era now unfolding before… Read More

Hot on the heels of DVConUS 2025, the 35th annual Synopsys User Group (SNUG) Conference made its mark as a defining moment in the evolution of Synopsys—and the broader electronic design automation (EDA) industry. This year’s milestone event not only underscored Synopsys’ continued innovation but also affirmed the vision… Read More

The 2025 Design and Verification Conference (DVCon) was a four-day event packed with insightful discussions, cutting-edge technology showcases, and thought-provoking debates. The conference agenda included a rich mix of tutorial sessions, a keynote presentation, a panel discussion, and an exhibit hall with Electronic… Read More

Unlike traditional software programming, AI software modeling represents a transformative paradigm shift, reshaping methodologies, redefining execution processes, and driving significant advancements in AI processors requirements.

Software Programming versus AI Modeling: A Fundamental Paradigm Shift

Traditional… Read More

Part 2 of 2 – Performance Validation Across Hardware Blocks and Firmware in SoC Designs

Part 2 explores the performance validation process across hardware blocks and firmware in System-on-Chip (SoC) designs, emphasizing the critical role of Hardware-Assisted Verification (HAV) platforms. It outlines the validation workflow… Read More

Part 1 of 2 – Essential Performance Metrics to Validate SoC Performance Analysis

Part 1 provides an overview of the key performance metrics across three foundational blocks of System-on-Chip (SoC) designs that are vital for success in the rapidly evolving semiconductor industry and presents a holistic approach to optimize… Read More

When contemplating the Lego-like hardware and software structure of a leading system-on-chip (SoC) design, a mathematically inclined mind might marvel at the tantalizing array of combinatorial possibilities among its hardware and software components. In contrast, the engineering team tasked with its validation may have… Read More

The Impact of AI on Software and Hardware Development

Part 4 of this series analyzes how AI algorithmic processing is transforming software structures and significantly modifying processing hardware. It explores the marginalization of the traditional CPU architecture and demonstrates how software is increasingly dominating… Read More

Chemical Origins of Environmental Modifications to MOR Lithographic Chemistry