Very Large Scale Integration (VLSI) engineering organizations are known for their intricate workflows that require high-performance simulation software and an abundance of simulation licenses to create cutting-edge chips. These workflows involve complex dependency trees, where one task depends on the completion of another… Read More

Author: Kalar Rajendiran

Synopsys Accelerates First-Pass Silicon Success for Banias Labs’ Networking SoC

Banias Labs is a semiconductor company that develops infrastructure solutions for next-generation communications. Its target market is the high-performance computing infrastructure market including hyperscale data center, networking, AI, optical module, and Ethernet switch SoCs for emerging high-performance computing… Read More

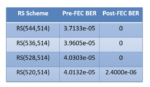

Mitigating the Effects of DFE Error Propagation on High-Speed SerDes Links

As digital transmission speeds increase, designers use various techniques to improve the signal-to-noise ratio at the receiver output. One such technique is the Decision Feedback Equalizer (DFE) scheme, commonly used in high-speed Serializer-Deserializer (SerDes) circuits to mitigate the effects of channel noise and … Read More

Optimizing Return on Investment (ROI) of Emulator Resources

Modern day chips are increasingly complex with stringent quality requirements, very demanding performance requirement and very low power consumption requirement. Verification of these chips is very time consuming and accounts for approximately 70% of the simulation workload on EDA server farms. As software-based simulators… Read More

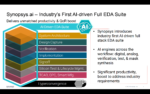

Full-Stack, AI-driven EDA Suite for Chipmakers

Semiconductor technology is among the most complex of technologies and the semiconductor industry is among the most demanding of industries. Yet the ecosystem has delivered incredible advances over the last six decades from which the world has benefitted tremendously. Yes, of course, the markets want that break-neck speed… Read More

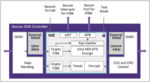

Securing Memory Interfaces

News of hackers breaking into systems is becoming common place these days. While many of the breaches reported to date may have been due to security flaws in software, vulnerabilities exist in hardware too. As a result, the topic of security is getting increased attention within the semiconductor industry around system-on-chip… Read More

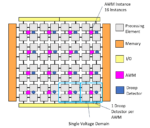

Adaptive Clock Technology for Real-Time Droop Response

In integrated circuit terminology, a droop is the voltage drop that happens in a circuit. This is a well-known phenomenon and can happen due to the following reasons. The power supply falls below the operating range for which a chip was designed for, resulting in a droop. More current is drawn by the conductive elements than they … Read More

The Rise of the Chiplet

The emergence of chiplets as a technology is an inflection point in the semiconductor industry. The potential benefits of adopting a chiplets-based approach to implementing electronic systems are not a debate. Chiplets, which are smaller, pre-manufactured components can be combined to create larger systems, offering benefits… Read More

Multi-Die Systems Key to Next Wave of Systems Innovations

These days, the term chiplets is referenced everywhere you look, in anything you read and in whatever you hear. Rightly so because the chiplets or die integration wave is taking off. Generally speaking, the tipping point that kicked off the move happened around the 16nm process technology when large monolithic SoCs started facing… Read More

Semiconductors and Mobile Communications: 5G and Beyond

Mobile World Congress (MWC) is the world’s largest gathering of mobile industry innovators where one can hear the latest on advanced technologies and solutions. This year, it took place from February 27 through March 2. Soitec was there to share their insights on how mobile communications are going to evolve with 5G and beyond … Read More

Siemens U2U 3D IC Design and Verification Panel