The creation of test patterns for mixed signal IP has been, to a large extent, a manual effort. To improve the process used to test, access, and control embedded IP, a new IEEE P1687 standard is being defined by a broad coalition of IP vendors, IP users, major ATE companies, and all three major EDA vendors. This new standard, also called… Read More

Author: glforte

Mentor and NXP Demonstrate that IJTAG Can Reduce Test Setup Time for Complex SoCs

Creating Plug-and-Play IP Networks in Large SoCs with IEEE P1687 (IJTAG)

Until now, the integration and testing of IP blocks used in large SOCs has been a manual, time consuming design effort. A new standard called IEEE P1687 (or “IJTAG”) for IP plug-and-play integration is emerging to simplify these tasks. EDA tools are also emerging to support the new standard. Last week mentor announcedTessent IJTAG,… Read More

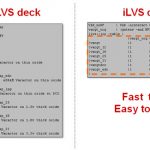

iLVS: Improving LVS Usability at Advanced Nodes

LVS Challenges at Advanced Nodes

Accurate, comprehensive device recognition, connectivity extraction, netlist generation and, ultimately, circuit comparison becomes more complex with each new process generation. As the number of layers and layer derivations increases the complexity of devices, especially Layout Dependent… Read More

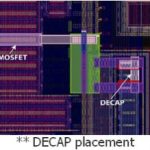

Improving Analog/Mixed Signal Circuit Reliability at Advanced Nodes

Preventing electrical circuit failure is a growing concern for IC designers today. Certain types of failures such as electrostatic discharge (ESD) events, have well established best practices and design rules that circuit designers should be following. Other issues have emerged more recently, such as how to check circuits… Read More

Parasitic Extraction—My Head Hurts!

By Carey Robertson, Director of Product Marketing, Mentor Graphics

IC physical verification requires a number of different types of checking, the most familiar being design rule checking (DRC), layout vs. schematic (LVS) checking, and parasitic extraction combined with circuit simulation. Fundamentally, it does not matter… Read More

New ERC Tools Catch Design Errors

A growing number of reports highlight a class of design errors that is difficult to check using more traditional methods, and can potentially affect a wide range of IC designs, especially where high reliability is a must.By Matthew Hogan

Today’s IC designs are complex. They contain vast arrays of features and functionality in … Read More

Computational Lithography, Scaling’s Best Friend

By Joseph Sawicki, Vice President & General Manager, Design to Silicon Division

It is one of the more amazing stories in the continued march of Moore’s Law over the past four nodes. Previously scaling was enabled solely though changes in the physical domain, whether through decreasing the wavelength of light, increasing … Read More

Mentor Company History

A venture capitalist offered the advice, “Startup investors are attracted by good people making a good product for a growing market.” That wisdom, as much as any served as the foundation for the company Mentor Graphics would become.… Read More

What Do You Mean by Mandatory?

When TSMC and Mentor Graphics held a joint seminar for mutual customers to go over new DFM requirements at 45/40 nm, two customers basically asked the same question, “What do you mean by mandatory?” Of course, TSMC wasn’t going to stand over them and say, “Mandatory means mandatory, what part of mandatory don’t you understand?” … Read More

What Do You Mean by Mandatory?

When TSMC and Mentor Graphics held a joint seminar for mutual customers to go over new DFM requirements at 45/40 nm, two customers basically asked the same question, “What do you mean by mandatory?” Of course, TSMC wasn’t going to stand over them and say, “Mandatory means mandatory, what part of mandatory don’t you understand?” … Read More

Breker Hosts an Energetic Panel on Spec-Driven Verification