Every industry has famous thought leaders that can summarize where we’ve been and then paint a picture of where we’re headed towards in the future. Often they make statements that become industry expressions, like “Moore’s Law” or the “Internet of Things”. I think that if Synopsys… Read More

Author: Daniel Payne

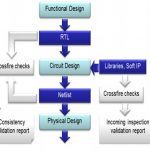

Digital, Analog, Software, IP – Isn’t it all just the same?

Designing an SoC requires a team, and the engineers typically use lots of specialized EDA software and semiconductor IP to get the job done. Many have started to ask about how designing a chip is different than designing and managing a large software project, or how is analog design different than digital design in terms of managing… Read More

Learning an HDL Simulator

Learning an HDL language or an HDL simulator are two different things, so I wanted to see what was available for learning a vendor-specific HDL simulator. I’ve already taught Verilog as an instructor using both ModelSim and Active-HDL simulators, however we only used a handful of commands in the class and labs in order to … Read More

Power and Thermal Simulation in ESL Verification Flows

At the recent DVcon there was a keen focus on design verification and validation. Much of the attention is on Logic/circuit design verification, UVM, and IP verification. At the system level functional verification has improved to comprehend complex hardware and software interaction using Virtual Platforms/SystemC and Transaction… Read More

Automobiles and DAC

On SemiWiki we have some 247 blogs and forum discussions on the topic of “automotive“, so I’m pleased to learn that at DAC in San Francisco there is a new track just for automotive systems and software. Just consider all of that electronic content in your typical auto:… Read More

Show Me How To Get Better DRC and LVS Results For My SoC Design

Most IC engineers learn best by hands-on experience when another more experienced person can show us what to do. If you cannot find that experienced person, then the next best thing is a video from an expert. I was surprised to find out that video was so important today that the #2 most viewed web site on the Internet was www.youtube.com… Read More

Addressing MCU Mixed Signal Design Challenges

The emerging market for IoT and wearable devices are designed with mixed-signal IP that includes: embedded CPU, flash, analogue and radio.EDA and IP companies have recently worked together to allow us to design an MCU with mixed-signal IP blocks more efficiently. This morning I attended a webinar with presenters from ARMand … Read More

A New, Free, Web-Based EDA Toolset in the Cloud

In the 1990’s there was a push to build EDA frameworks, however they all failed because no user wanted to be locked into one EDA vendor tool flow. Fast forward to 2014 and there’s an emerging trend to use web-based EDA tools as a framework, instead of downloading and installing software to your desktop or device. I just… Read More

A New Digital Place and Route System

IC place and route tools can be very high-priced EDA software to purchase or lease, so there’s some good news for AMS designers that need an affordable digital place and route tool for their mostly analog designs. Today the team at Tanner EDAannounced a totally new place and route system has been added to their Schematic Driven… Read More

Semiconductor IP Validation Gets Faster

Semiconductor IP continues to grow in use for SoC design, and many chips can now use hundreds of IP blocks from multiple vendors. Validating the quality of the IP blocks is an important step in the design process, and you could perform manual validation and inspection of each new IP block at the expense of time and engineering effort.… Read More

Intel, Musk, and the Tweet That Launched a 1000 Ships on a Becalmed Sea