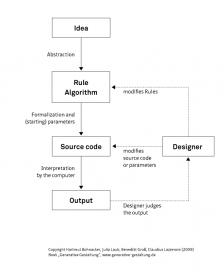

Scanning headlines of technology news every day I was somewhat familiar with the phrase “Generative Design” and even browsed the Wikipedia page to find this informative flow-chart that shows the practice of generative design.

Generative design is an iterative design process that involves a program that will generate… Read More

Captain America: Can Elon Musk Save America’s Chip Manufacturing Industry?