Our laptops and desktop computers have billions of transistors in their application processor chips, yet I often don’t consider the reliability effects of aging that the transistors experience in the chips. At the recent Synopsys User Group (aka SNUG), there was a technical presentation on this topic from Srinivas Bodapati,… Read More

Author: Daniel Payne

Using EM/IR Analysis for Efinix FPGAs

I’ve been following the EM/IR (Electro-Migration, IR is current and resistance) analysis market for many years now, and recently attended a presentation from Steven Chin, Sr. Director IC Engineering of Efinix, at the User2User event organized by Siemens EDA. The Tuesday presentation was in the morning at the Marriott… Read More

Methods for Current Density and Point-to-point Resistance Calculations

IC reliability is an issue that circuit design engineers and reliability engineers are concerned about, because physical effects like high Current Density (CD) in interconnect layers, or high point-to-point (P2P) resistance on device interconnect can impact reliability, timing or Electrostatic Discharge (ESD) robustness.… Read More

3D IC Update from User2User

Our smart phones, tablets, laptops and desktops are the most common consumer products with advanced 2.5D and 3D IC packaging techniques. I love seeing the product tear down articles to learn how advanced packaging techniques are being used, so at the User2User conference in Santa Clara I attended a presentation from Tarek Ramadan,… Read More

Joseph Sawicki of Siemens EDA at User2User

I attended the annual user group meeting called User2User in Santa Clara this year, hosted by Siemens EDA, with 51 presentations by customers in 11 tracks, and keynotes during each lunch hour from semiconductor executives. Joseph Sawicki, Executive VP, IC Segment, at Siemens EDA presented on a Tuesday, along with Prashant Varshney,… Read More

Cybersecurity Threat Detection and Mitigation

Every week in the technology trade press I am reading about cybersecurity attacks against web sites, apps, IoT devices, vehicles and even ICs. At the recent IP SoC Silicon Valley 2022 event in April I watched a cybersecurity presentation from Robert Rand, Solution Architect for Tessent Embedded Analytics at Siemens EDA. Common… Read More

High-speed, low-power, Hybrid ADC at IP-SoC

Andrew Levy and I both worked at Intel and Opmaxx, and I knew that he was now working at Alphacore, an IP company specializing in mixed-signal, RF, imaging and rad-hard applications. I was curious what Alphacore was up to, so at the IP-SoC Silicon Valley 2022 event I watched the ADC presentation from Ken Potts, COO of Alphacore. Mr.… Read More

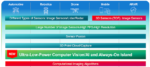

Designing Ultra-Low-Power, Always On IP

It’s popular to use DSP chips for vision processing in diverse applications like ADAS, security cameras and AR. Tensilica has been designing DSP chips and IP since 1997, and their technology was successful enough that Cadence acquired Tensilica back in 2013. At the IP-SoC Silicon Valley 2022 event in April I had the pleasure… Read More

Efficient Memory BIST Implementation

Test experts use the acronym BIST for Built In Self Test, it’s the test logic added to an IP block that speeds up the task of testing by creating stimulus and then looking at the output results. Memory IP is a popular category for SoC designers, as modern chips include multiple memory blocks for fast, local data and register storage… Read More

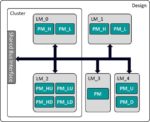

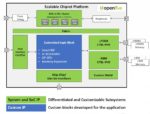

IP Subsystems and Chiplets for Edge and AI Accelerators

From a business viewpoint we often read in the technical press about the virtues of applying AI, and in the early days most of the AI model building was done in the cloud, because of the high computation requirements, yet there’s a developing trend now to use AI accelerators at the Edge. The other mega-trend in the past decade… Read More

Captain America: Can Elon Musk Save America’s Chip Manufacturing Industry?