At advanced nodes, design rules are necessarily more complex and restrictive. Although most of the time you can find a way to live with them, sometimes it’s necessary to seek a waiver from the foundry for a particular design feature. This involves documenting the feature, the design rules in question and the conditions under which… Read More

Author: Beth Martin

An easier way to deal with design rule waivers (video)

Catch Mentor’s embedded sessions at ARM TechCon

For Halloween this year, why not tell your embedded software debug horror stories at ARM TechCon? Mentor will have several campfire sessions you should consider attending, but here my Halloween thread breaks down. These three sessions are all quite cheery.

This one, Software Debug on ARM Processors in Emulationis on using emulation… Read More

Mentor Seminar: Evolution of diagnosis-driven yield analysis

It’s a fact that new process nodes come with some amount of yield challenges. One way to find and eliminate silicon defects is through diagnosis-driven yield analysis (DDYA), which is the topic of a free seminar by Mentor Graphics in Fremont this Thursday, October 10 from 11:30am – 2pm (yes, lunch is included because Mentor… Read More

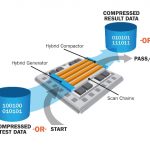

What Mentor Said at ITC

At the ITC test conference in early September, Mentor made three announcements. ITC is a big event for Mentor’s test group, and where they usually roll out their new tools and capabilities. The indefatigable Steve Pateras was captured on film describing them.

I’ve summarize Mentor’s three announcements and added… Read More

Testing an IC Sandwich

At a lovely, but chilly, 3DIncites awards breakfast during SEMICON West, I saw Mentor Graphics win in two of five categories (Calibre 3DSTACK was the other winner). Afterwards, I talked to Steve Pateras, the product marketing director of Mentor’s test solutions about Tessent Memory BIST, which was one of the winners. I asked Pateras… Read More

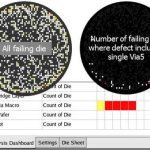

A Goldmine of Tester Data

Yesterday at SEMICON West I attended an interesting talk about how to use the masses of die test data to improve silicon yield. The speaker was Dr. Martin Keim, from Mentor Graphics.

First of all, he pointed out that with advanced process nodes (45nm, 32nm, and 28nm), and new technologies like FinFETs, we get design-sensitive defects.… Read More

Free Pass to SEMICON West!

SEMICON West is next week, July 9-11 in San Francisco. If you haven’t signed up, and want to attend for free instead of $100,

1) Send an email to silicon_test@mentor.com with subject line “Semicon pass.”

2) Register for SEMICON West

3) After registering, download the SEMICON West mobile app and start building your schedule. Here… Read More

DAC lunch seminar: Better IP Test with IEEE P1687

What: DAC lunch seminar (register here)

When: June 5, 2013, 11:30am – 1:30pm

Where: At DAC in lovely Austin, TX

Dr. Martin Keim of Mentor Graphics will present this overview of the new the IEEE P1687 standard, called IJTAG for ‘internal’ JTAG.

If you are involved in IC test*, you’ve probably heard about IJTAG. If you … Read More

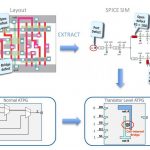

Cell-Aware Test Seminar

You may have heard about cell-aware testing. It’s a transistor-level test (ATPG) methodology that is quickly becoming a hot topic. If you are involved in DFT and are looking for better quality and reliability, you should definitely know about cell-aware testing.

And lucky you, on May 16, 2013, you can attend a free seminar on cell-aware… Read More

Mentor Graphics’ Best User2User Ever

Calling all Mentor users! Don’t forget to register for the U2U in San Jose on Thursday, April 25.

In addition to three worthy keynotes, you will find a more interactive and solution-focused day than in the past. There are sessions on place & route, custom/AMS, emulation, test and yield analysis, functional verification, Calibre… Read More

Solving the EDA tool fragmentation crisis