You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

While it’s interesting to hear a tool-vendor’s point of view on the capabilities of their product, it’s always more compelling to hear a customer/user point of view, especially when that customer is NVIDIA, a company known for making monster chips.

A quick recap on the concept. At 7nm, operating voltages are getting much closer… Read More

I was driving recently on highway 87 (San Jose) and wanted to merge left. I checked my side-mirror, checked the blind-spot detector, saw no problems and started to move over – and quickly swerved back when a car shot by on my left. What went wrong? My blind-spot detection, a primary feature in ADAS (advanced driver assistance systems,… Read More

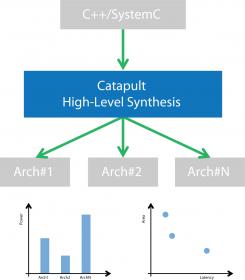

Automotive markets have added pressure on semiconductor/systems design through demand for ISO26262 compliance – this we all know. But they have also changed the mix of important design types. Once class of design that has become very significant in ADAS, and ultimately autonomous applications, is image signal processing (ISP).… Read More

For any given design objective, there is what we in the design automation biz preach that design teams should do, and then there’s what designs teams actually do. For some domains, the gap between these two may be larger than others, but we more or less assume that methodologies which have been around for years and are considered to… Read More

The DIY Syndromeby Bernard Murphy on 11-09-2017 at 7:00 amCategories: Aldec, EDA

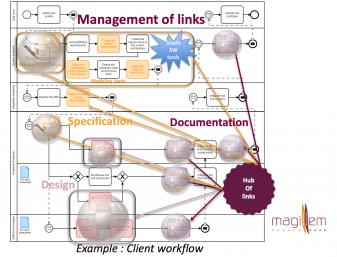

When facing a new design objective, we check off all the established tools and flows we know we are going to need. For everything else, we default to an expectation that we will paper over the gaps with scripting, documentation and spreadsheets. And why not? When we don’t know what we will have to deal with, in documentation, scheduling,… Read More

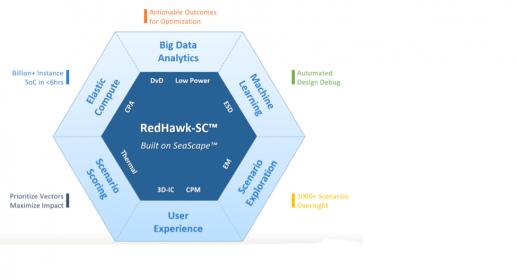

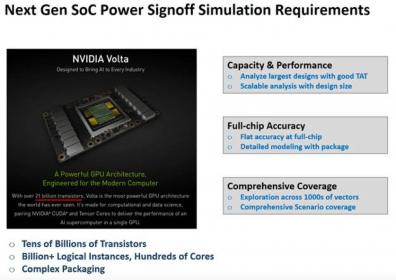

Want to know how NVIDIA signs off on power integrity and reliability on mega-chips? Read on.

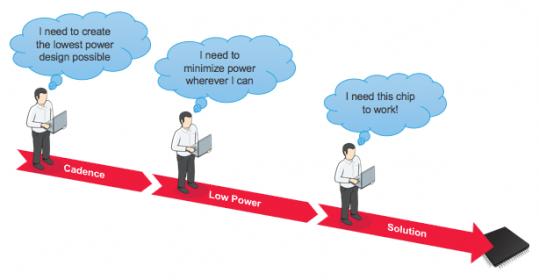

PPA over-design has repercussions in increased product cost and potential missed schedules with no guarantee of product success. Advanced SoCs pack more functionality and performance resulting in higher power density, but traditional… Read More

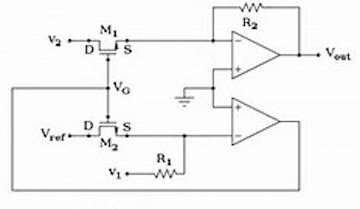

Power integrity and reliability are just as important for AMS designs as they are for digital designs. Ansys is offering a series of five webinars on this topic, under a heading they call ANSYS in ACTION, a bi-weekly demo series from ANSYS in which an application engineer shows you how simulation can address common applications.… Read More

We have an urge to categorize companies, and when our limited perspective is of a company that helps with design, we categorize it as an EDA company. That was my view of Magillem, but I have commented before that my view is changing. I’m now more inclined to see them more as the design equivalent of a business intelligence organization… Read More

Despite all the enthusiastic discussion about security in the IoT and a healthy market in providers of solutions for the same, it is difficult to believe that we are doing more than falling further behind an accelerating problem. Simon Segars echoed this in his keynote speech at ARM TechCon this year. The issue may not be so much in… Read More

You don’t shower only before you have to go to an important meeting (teenagers excepted). Surgical teams go further, demanding a strict regimen of hygiene be followed before anyone is allowed into an operating room. Yet we tend to assume that libraries and physical IP (analog, memories, other physical blocks) are checked and pronounced… Read More

Intel, Musk, and the Tweet That Launched a 1000 Ships on a Becalmed Sea