For decades, chip design has been a delicate balance of creativity and drudgery. Architects craft detailed specifications, engineers read those documents line by line, and teams write and debug thousands of lines of Verilog and UVM code. Verification alone can consume up to 35 percent of a project’s cost and add many months to the schedule.

Moores Lab(AI), a young company founded by veterans of chip engineering and artificial intelligence, believes the era of “manual everything” is ending. Its vision is agentic AI that not only assists engineers but actively orchestrates the entire pre-fabrication workflow—from architecture specification all the way to a verified GDSII hand-off.

At the AI Infra Summit 2025, I interviewed Shelly Henry, the founder of Moores Lab(AI). Following is a synthesis of that conversation.

The Spark Behind Agentic AI

The founders’ “aha” moment came when they recognized that large language models could finally tackle what had always been an understanding problem, not merely an automation problem. Before modern AI, no tool could read a specification document, truly comprehend it, and then translate that intent into correct, production-ready RTL or UVM code.

Today Moores Lab(AI) can do exactly that. Its platform reads and interprets a specification much like a human designer, generates Verilog and UVM code, and iterates automatically until the design compiles cleanly. It integrates with industry-standard verification suites—Synopsys VCS, Cadence Xcelium, Siemens Questa, and others—fixing issues as it goes. The goal is not to replace EDA tools but to remove the manual glue work that has held the process together for decades.

Middleware on the Backend, Automation on the Frontend

Moores Lab(AI)’s technology works like a two-sided engine. On the backend it serves as middleware that ties together heterogeneous EDA tools and manages constraints, switches, and re-runs—tasks that once required endless scripting. On the frontend it tackles the most labor-intensive work: writing Verilog, building UVM testbenches, debugging, and optimizing for power, performance, and area. This combination makes the platform both an orchestration layer and an agentic AI assistant.

Three Operating Modes for Real-World Designs

A system-on-chip rarely begins from a clean slate. Some blocks are reused, others need modification, and some must be built from scratch. Moores Lab(AI) trains its agent tools to mirror that reality with three operating modes: “Scratch” for brand-new IP blocks, “Edit” to modify existing designs, and “Complete” to integrate third-party or legacy IP unchanged. Engineers simply declare the status of each block and the platform selects the right strategy.

Measurable, Independent Productivity Gains

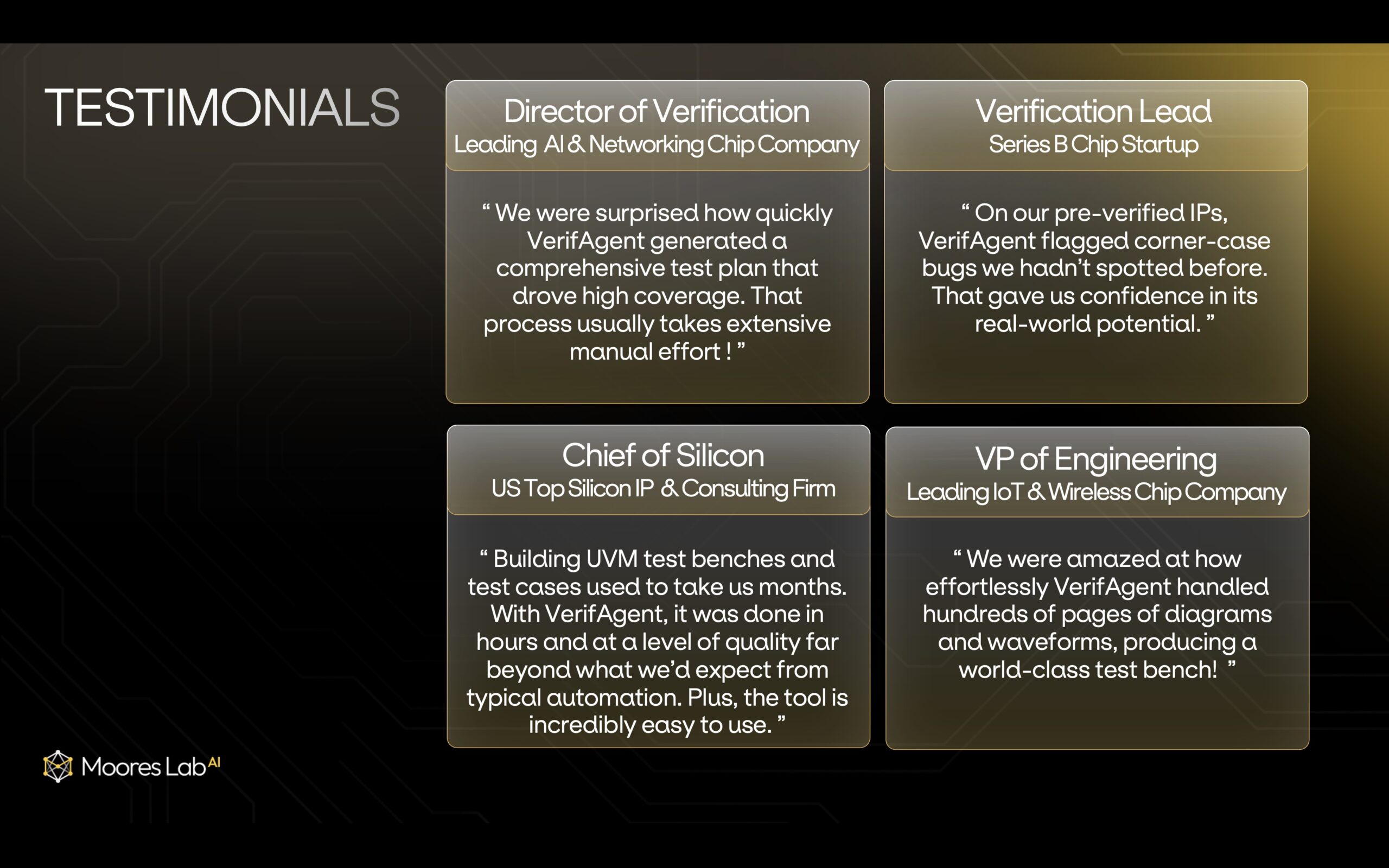

According to the company, customer pilots using Moores Lab(AI)’s VerifAgent™ have shown striking improvements. Creating a test plan that once took three weeks can now be done in about ten minutes. Building a testbench that typically required three months can be completed in less than a day. Implementing test cases, which used to take two to three months, can also be finished in a single day. These results translate to productivity improvements of roughly 92 to 97 percent and schedule accelerations of seven to ten times, even before full SoC automation is available. Current tools focus on digital blocks, with analog support on the roadmap.

Security and Control Built In

Customer intellectual property protection is paramount. All Moores Lab(AI) tools run on-premises or in a customer’s private cloud. The LLM connection is entirely under the customer’s own subscription—Azure, OpenAI, Anthropic Claude, Google Gemini, or another provider. EDA licenses remain customer-owned. Moores Lab(AI) never sees customer data, making the platform a self-contained, enterprise-grade solution.

As I Was Finishing My Interview

As I was finishing my interview with Shelly, I realized a value proposition that may be hiding within Moores Lab(AI)’s technology. Many semiconductor companies have historically locked into a predominantly single-vendor EDA flow for valid reasons—licensing simplicity, team expertise, and risk management among them. That approach, however, limits flexibility and can force compromises on tool quality.

What if there were a painless way to enable easy mix-and-match of EDA tools on a project-by-project or design-by-design basis? I asked Shelly if that was possible, and he affirmed it and elaborated.

Freedom to Mix and Match EDA Tools More Easily

With a few configuration settings, engineering teams can create bespoke multi-vendor flows for every chip or block, choosing the best simulator, synthesizer, or place-and-route engine for each project. Traditionally, achieving this kind of heterogeneity required weeks of fragile scripting and complex license management. Moores Lab(AI) abstracts those differences, making the process almost plug-and-play. The implications are significant: easier adoption of best-in-class tools, reduced vendor lock-in, and even new leverage when negotiating future EDA license deals.

A Complement, Not a Competitor

Crucially, Moores Lab(AI) does not replace core EDA engines such as synthesis or place-and-route. It layers on top, automating the manual tasks that once linked those engines together. That makes partnerships—not displacement—the natural relationship with incumbents such as Synopsys, Cadence, and Siemens.

Looking Ahead

Over the next three to five years, Moores Lab(AI) expects agentic AI to extend across RTL, verification, and backend flows with growing autonomy, while humans remain essential for architectural decisions and final sign-off. Longer term, fully automated design is conceivable but will always require human oversight.

Summary

Whether customers adopt it first for the eye-catching seven-to-ten-times schedule acceleration or for the newfound ability to tailor EDA workflows to each project, Moores Lab(AI) is quietly re-architecting how chips are built. For an industry eager to shorten design cycles, cut costs, and escape vendor lock-in, that combination may be transformative.

Also Read:

AI Everywhere in the Chip Lifecycle: Synopsys at AI Infra Summit 2025

Neurosymbolic code generation. Innovation in Verification

Podcast EP308: How Clockwork Optimizes AI Clusters with Dan Zheng

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.