The march toward higher-speed networking continues to be guided by the same core objectives as has always been : increase data rates, lower latency, improve reliability, reduce power consumption, and maintain or extend reach while controlling cost. For the next generation of high-speed interconnects, these requirements are embodied in the development of 448G high-performance SerDes. This will serve as the foundational electrical layer for scaling Ethernet beyond 1.6T, while also enabling other advanced interconnect architectures in AI, storage, and cloud-scale computing.

Meeting the core objectives has become progressively more complex with each generation. Today’s challenges include the diverging performance needs of AI and general networking applications, the distinct technical contributions of multiple standards organizations, and the growing sophistication required in electrical PHY implementations to meet 448G signaling requirements. The push for 448G is taking place in a context where the industry is both motivated to move quickly and tasked with solving a broader set of technical and deployment variables than ever before.

Synopsys provided a status update on this very topic, during a webinar it hosted recently. The webinar was delivered by Kent Lusted, Distinguished Architect and Priyank Shukla, Director of Product Management. This webinar is now accessible on-demand from here.

Industry Readiness and Market Drivers

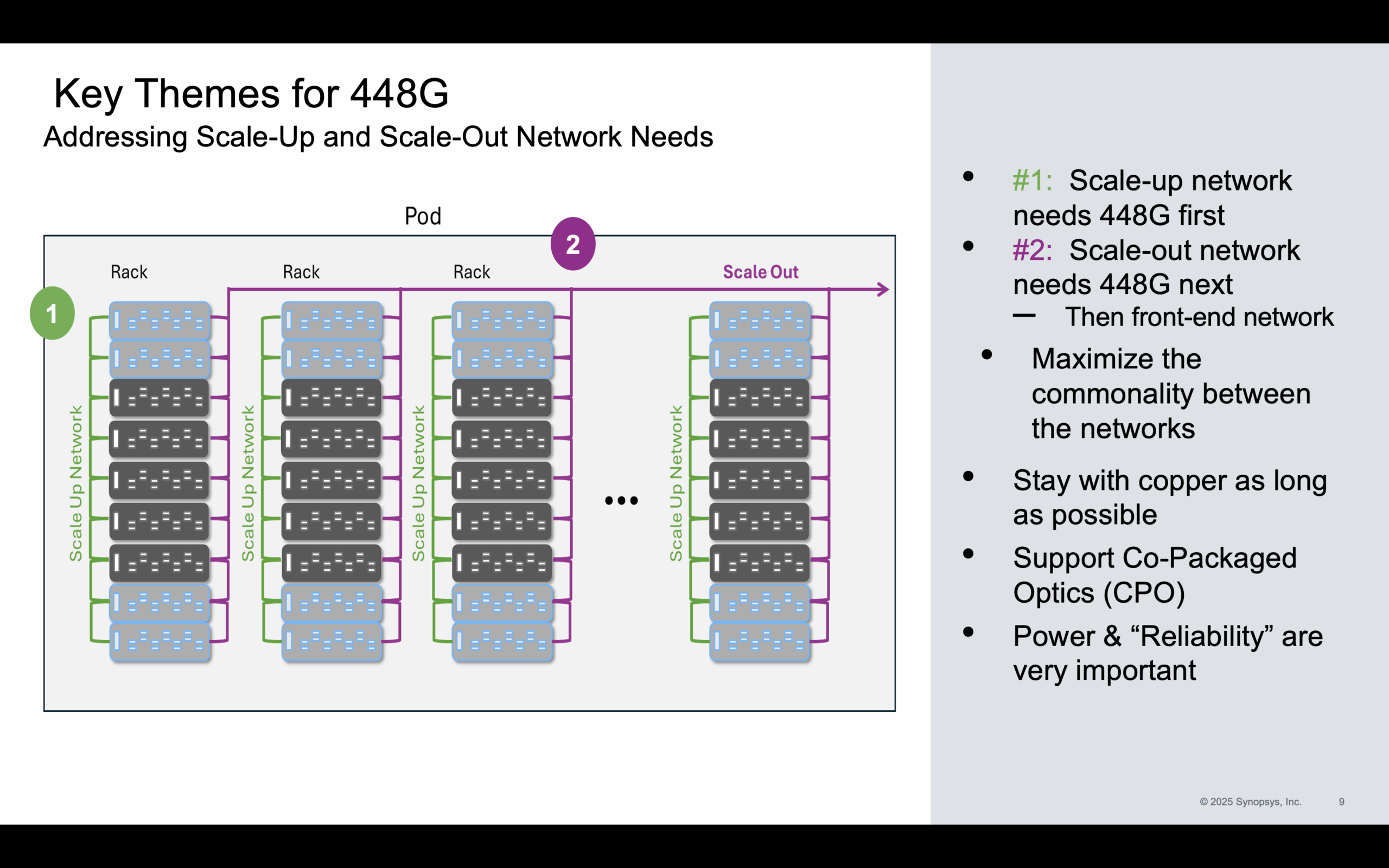

The readiness for 448G Electrical PHY adoption is high, particularly in AI-driven scale-up and scale-out data center networks where back-end interconnect bottlenecks are already limiting system performance. Operators in these environments are pressing for faster rates with minimal latency and power, making 448G the logical next step. Hyperscalers and large enterprise operators are preparing infrastructure roadmaps that anticipate both short-reach copper-based implementations and longer-reach optical deployments.

From a supply chain perspective, SerDes technology at 224G per lane — the immediate precursor to 448G dual-lane architectures — has matured rapidly, providing a strong technical foundation. This maturity enables early prototyping of 448G PHYs, ensuring that when the standards are finalized, both silicon and system designs will be ready for deployment.

Emerging Standards and Collaborative Progress

Multiple standards bodies are actively shaping the path to 448G Electrical PHYs. The Optical Internetworking Forum (OIF) launched its CEI-448G framework project in July 2024, setting the stage for defining channel characteristics, modulation targets, and reach objectives. The IEEE P802.3dj task force is extending Ethernet standards to 1.6T and 200G-per-lane, with 448G PHYs as critical building blocks. The Ultra Ethernet Consortium (UEC) and UALink are aligning electrical interface specifications with AI-scale fabric requirements, while the Storage Networking Industry Association (SNIA) is hosting workshops to converge perspectives from AI, storage, and networking domains. The Open Compute Project (OCP) continues to drive deployment-oriented specifications, addressing form factors, integration models, and operational considerations for hyperscale adoption.

This collaborative landscape ensures that the final specifications will be both technically robust and deployment-ready, even as each organization brings a unique emphasis—be it Ethernet protocol compliance, electrical interoperability, electro-optical links, AI optimization, or system integration.

Advanced Modulation Schemes

Selecting the optimal modulation for 448G is one of the most significant technical decisions in PHY design. The primary candidates—PAM4, PAM6, CROSS-32, DSQ-32, PR-PAM4, BiDi-PAM4, SE-PAM4, and DMT—offer varying trade-offs between bandwidth efficiency, signal-to-noise ratio, complexity, and compatibility.

PAM4 remains attractive for its backward compatibility and alignment with optical implementations, though it demands higher circuit bandwidth. PAM6 offers some bandwidth relief but at the cost of more complex DSP and reduced noise margin. Two-dimensional constellations like CROSS-32 and DSQ-32 can improve detector margin for certain symbol patterns but require even more sophisticated detection algorithms. Other approaches, such as BiDi-PAM4 and SE-PAM4, aim to maintain I/O count while introducing new signal recovery challenges. The final modulation choice—or set of choices—must balance implementation feasibility with performance goals across AI and non-AI environments.

Next-Generation Channel Designs

Channel topology is a critical determinant of PHY performance at 448G. AI-oriented deployments tend to favor short, low-loss paths such as direct attach copper cables, near-package interconnects, or co-packaged optics (CPO), which simplify equalization and reduce latency. In contrast, front-panel optical modules in general networking often require longer PCB traces, multiple connectors, and possibly retimers, all of which increase signal degradation and complexity in the receiver.

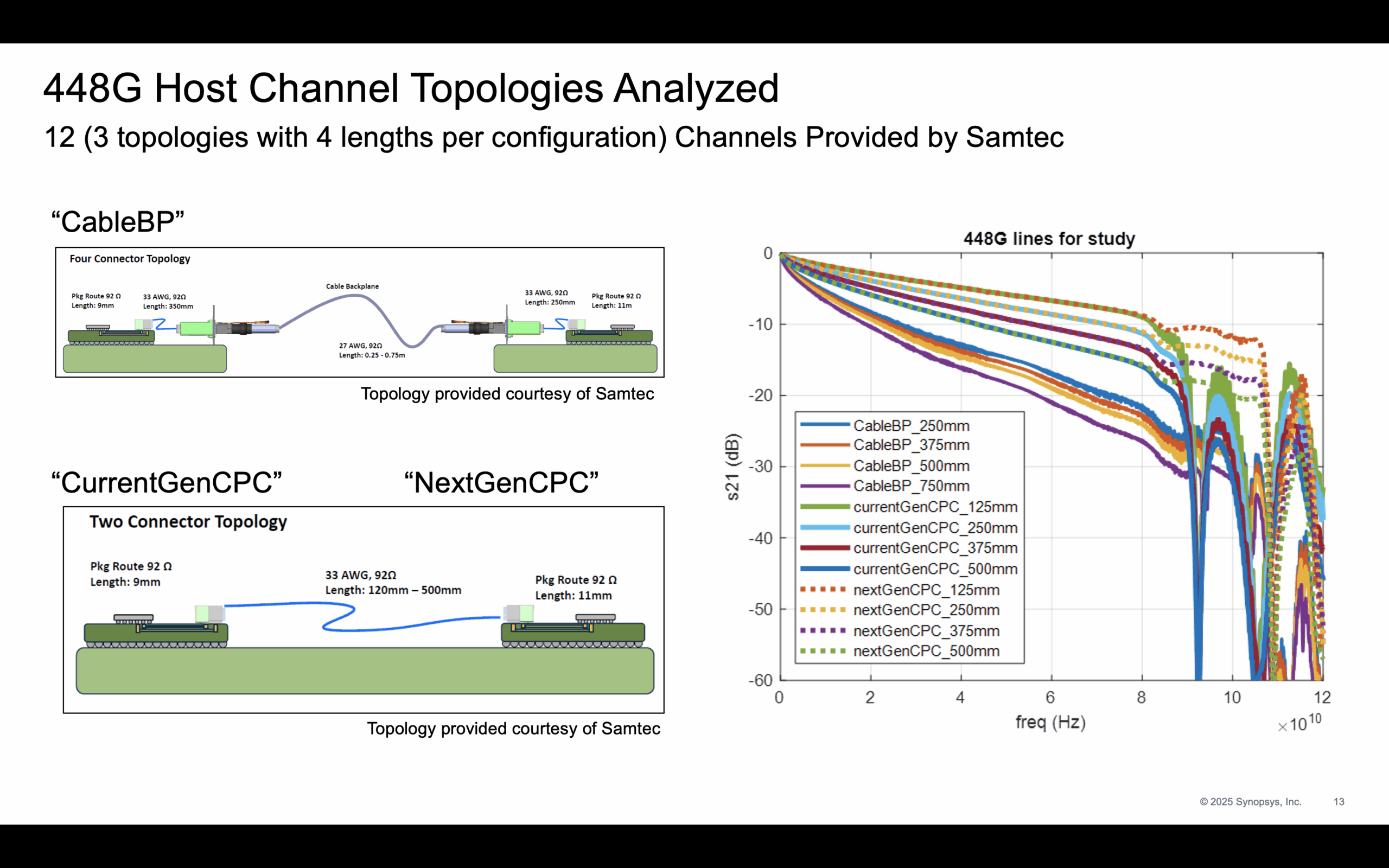

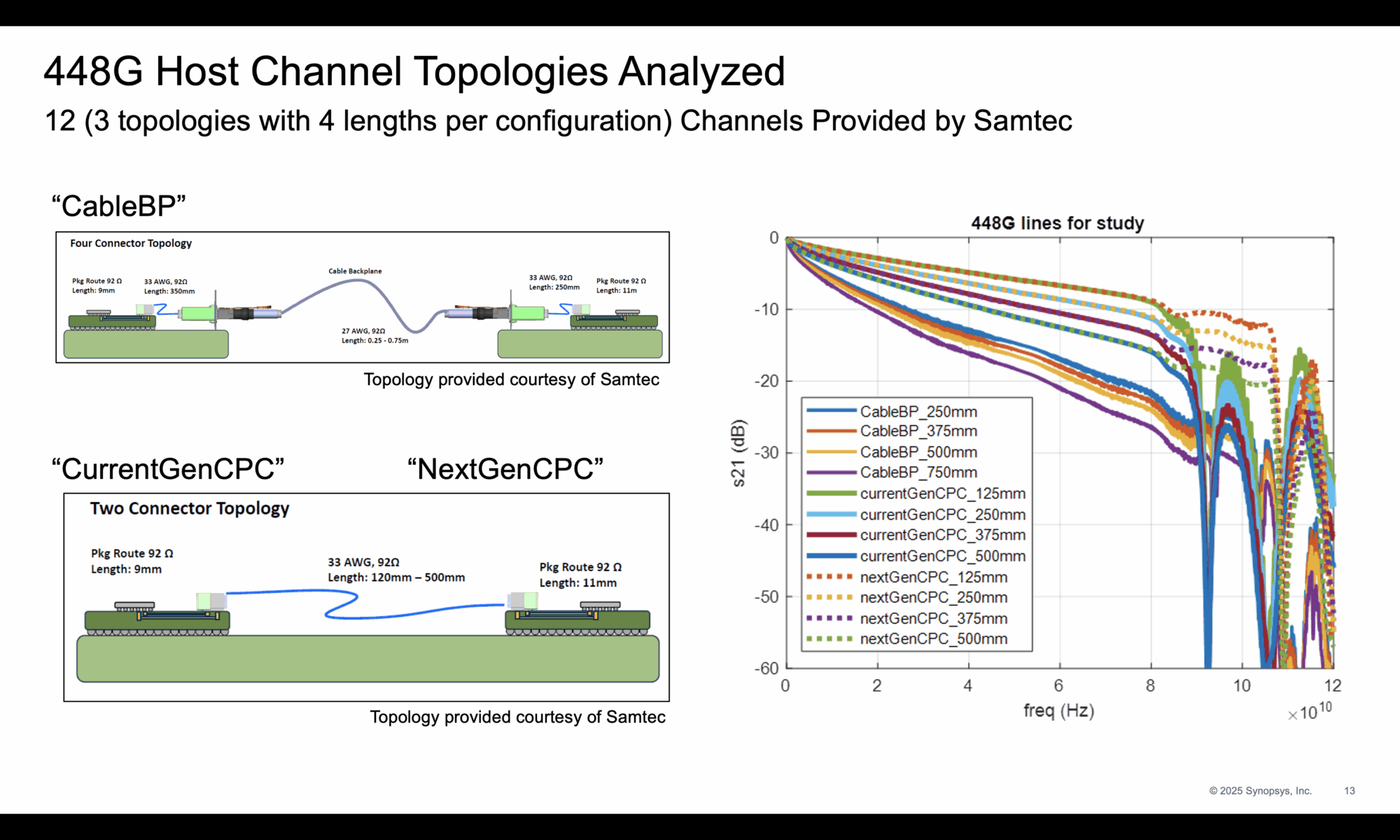

Synopsys’ analysis of 12 channel topologies, in collaboration with Samtec, evaluated performance under realistic conditions including crosstalk, jitter, noise, and ratio level mismatch (RLM). These results inform the specification process by showing how PAM4 and PAM6 modulationschemes perform across a range of physical configurations, ensuring that reach and margin targets are grounded in actual channel behavior.

Design Complexity in 448G Electrical PHYs

Implementing a 448G PHY in SerDes form involves overcoming significant design challenges. At such high data rates, unit intervals are extremely short, requiring precise timing recovery, advanced feed-forward and decision-feedback equalization, and high-resolution ADC/DAC operation. Moving from PAM4 to PAM6, for instance, increases the number of symbol transitions from 16 to 36, the number of comparators in an unrolled DFE from 16 to 36, and the detector bit width from 2 bits to 3 bits, all of which demand higher precision and potentially higher power. These realities must be considered alongside the modulation choice, packaging strategy, and thermal constraints. No clear implementation advantage for either approach has been identified as of date.

Synopsys’ Role in Accelerating 448G Development

Synopsys is contributing to accelerated 448G development by engaging across all major forums—IEEE, OIF, UEC, SNIA, and OCP—ensuring that data, insights, and perspectives are shared early and often. The company’s early studies on channel topologies, combined with in-depth analysis of modulation trade-offs and DSP architecture complexity, give standards bodies a concrete basis for narrowing options quickly.

By promoting a phased approach that will help deliver the right PHYs and interfaces “just in time”, Synopsys helps ensure that high-priority deployments can begin without waiting for the complete standards suite to mature. This strategy, combined with technical modeling, real-world measurements, and active ecosystem engagement, positions Synopsys as a key enabler of the industry’s transition to 448G Electrical PHYs.

Also Read:

Synopsys Webinar – Enabling Multi-Die Design with Intel

cHBM for AI: Capabilities, Challenges, and Opportunities

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.