The demand for high-performance and sustainable computing and networking silicon for AI has undoubtedly increased R&D dollars and the pace of innovation in semiconductor technology. With Moore’s Law slowing down at the chip level, there is a desire to pack as many chiplets as possible inside ASIC packages and get the benefits of Moore’s Law at the package level.

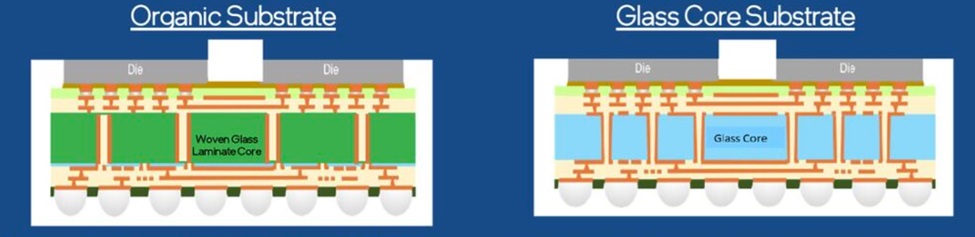

The ASIC package hosting multiple chiplets typically consists of an organic substrate. This is made from resins (mostly glass-reinforced epoxy laminates) or plastics. Depending on packaging technology, either the chips are mounted directly on the substrate, or there is another layer of silicon interposer between them for high-speed connectivity between the chiplets. Interconnect bridges instead of interposers are sometimes embedded inside the substrate to provide this high-speed connectivity.

The problem with organic substrates is that they are prone to warpage issues, especially in larger package sizes with high chip densities. This limits the number of dies that can be packed inside a package. That is where substrates made of glass could be game changers!

Advantages of Glass Substrates

✔ They can be made super flat, allowing for finer patterning and higher (10x) interconnect densities. During photolithography, the entire substrate receives uniform exposure, reducing defects.

✔ Glass has a similar thermal expansion coefficient as the silicon dies above it, reducing thermal stress.

✔ They don’t warp and can handle much higher chip density in a single package. Initial prototypes could handle 50% more chip density than organic substrates.

✔ Could seamlessly integrate optical interconnects, giving rise to more efficient co-packaged optics.

✔ These are typically rectangular wafers, which increase the number of chips per wafer, improving yield and reducing costs.

Glass substrates could potentially replace organic substrates, silicon interposers, and other high-speed embedded interconnects inside the package.

However, there are some challenges: Glass is brittle/fragile and prone to fractures during manufacturing. This fragility needs careful handling and specialized equipment to prevent damage during manufacturing processes. Ensuring proper adhesion between glass substrates and other materials used in semiconductor stacks, such as metals and dielectrics, is challenging. The differences in material properties can lead to stresses at the interfaces, potentially causing delamination or other reliability issues. While glass has a thermal expansion coefficient similar to silicon, it can differ significantly from materials used in PCB boards/bumps. This mismatch can cause thermal stresses during temperature cycling, impacting reliability and performance.

Lack of established industry standards for glass substrates leads to variability in performance across different vendors. As the technology is new, there is not enough long-term reliability data. More accelerated life testing is needed to gain confidence in using these packages for high-reliability applications.

Despite the disadvantages, glass substrates hold great promise for HPC/AI and DC networking silicon, where the focus is on packing as much throughput as possible inside ASIC packages to increase the overall scale, performance, and efficiency of the systems.

Major foundries like Intel, TSMC, Samsung, and SKC are heavily investing in this technology. Intel is leading the pack with test chips introduced late last year. However, it will be another 3-4 years before this inevitable transition to glass substrates happens for high-end silicon.

I can’t wait to see more innovations that push the boundaries of technology!

Also Read:

Intel Ushers a New Era of Advanced Packaging with Glass Substrates

Intel’s Gary Patton Shows the Way to a Systems Foundry #61DAC

TSMC Advanced Packaging Overcomes the Complexities of Multi-Die Design

Share this post via:

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center