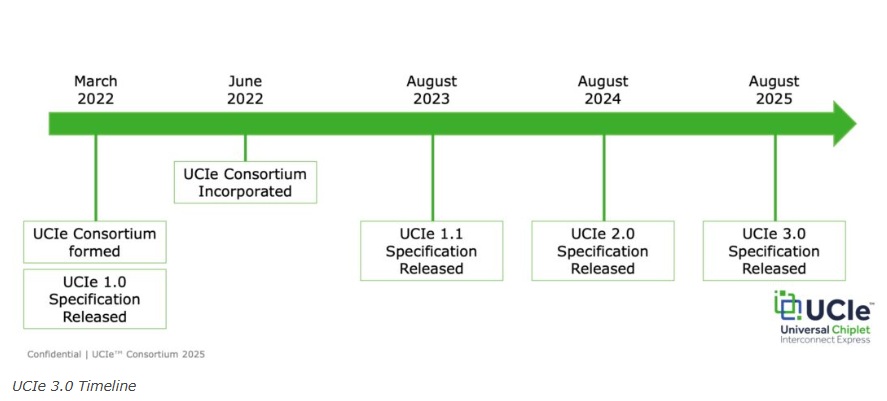

UCIe 3.0 is the third major revision of the open, die-to-die interconnect standard for chiplets inside a package. Announced August 5, 2025, UCIe 3.0 doubles peak link speed over 2.0—introducing 48 GT/s and 64 GT/s modes—while adding manageability, power-efficiency, and reliability features aimed at scaling multi-die systems for AI, HPC, and networking.

What’s new in 3.0

-

Higher data rates: New 48/64 GT/s options for both UCIe-S and UCIe-A, targeting higher bandwidth density at low power.

-

Runtime recalibration: Links can retune during operation (reusing init states) to sustain efficiency as conditions change.

-

Extended sideband reach: Sideband channel range extended up to 100 mm to support larger/more flexible SiP topologies.

-

Fast bring-up & control plane:

-

Early firmware download standardized over Management Transport Protocol (MTP).

-

Priority sideband packets for deterministic, low-latency events.

-

Fast-throttle & emergency shutdown for immediate system-wide notifications via open-drain I/O.

-

-

Continuous-transmission support: Raw-Mode mappings permit uninterrupted data flows (e.g., SoC–DSP).

-

Backward compatibility: 3.0 remains fully backward compatible with earlier UCIe versions.

Rationale and scope

The specification targets higher bandwidth density, lower power per bit, and stronger system-level manageability to accelerate multi-die SiP designs as AI and heterogeneous computing expand.

Manageability & lifecycle features

-

Initialization: Early firmware download over MTP shortens bring-up and standardizes fleet boot flows.

-

Deterministic control traffic: Priority sideband ensures time-critical messages arrive with minimal latency.

-

Safety hooks: Fast-throttle and emergency shutdown enable coordinated responses to thermal/power faults.

-

Design flexibility: Many manageability elements are optional, so implementers adopt what they need without extra silicon.

Physical/link enhancements

-

Runtime recalibration re-uses trained states to minimize power and downtime when re-tuning.

-

Sideband reach to 100 mm widens supported topologies across bigger packages or spread-out tiles.

Ecosystem & availability

The UCIe Consortium is led by major compute, cloud, and semiconductor companies and “represents more than 150 member companies.” The 3.0 spec is publicly available by request on the Consortium site; launch activities included sessions at FMS 2025 in Santa Clara.

Notable quotes

“UCIe 3.0 represents a critical step forward for the chiplet industry, delivering the speed, efficiency, and manageability needed to scale multi-chip designs.” — Cheolmin Park, UCIe Consortium President (Samsung Electro-Mechanics)

“The UCIe 3.0 specification marks a significant leap forward… With new link speeds of 48 GT/s and 64 GT/s…” — Ashish Karandikar, VP of Engineering, NVIDIA

“UCIe 3.0 advances chiplet interconnect with higher bandwidth, lower latency, and enhanced system manageability…” — Dimitrios Ziakas, VP & GM, Intel

“UCIe 3.0… enables up to 64 GT/s… necessary for future AI designs.” — Kevin Donnelly, VP of Strategic Marketing, Eliyan

“64 GT/s arrives at the perfect moment as AI infrastructure explodes… foundation for disaggregated, modular architectures at rack scale.” — Casey Morrison, CPO, Astera Labs

“Increased bandwidth rates to 48 and 64 GT/s… critical to addressing the growing interconnect bandwidth demands of GPUs and ASICs in AI.” — Vladimir Stojanovic, CTO, Ayar Labs

“Vendor-defined signals and Variable Rate support broaden UCIe’s applicability to real-time streaming… suited for RF data converters.” — Henil Langalia, Analog Devices / JESD204E chair

“With UCIe 3.0, we’re enabling customers to achieve greater bandwidth and density in larger, more efficient SiP designs…” — Ben Hyo Gyuem Rhew, Samsung Electronics

Design/implementation notes

-

Performance targets: 3.0 doubles 2.0’s 32 GT/s ceiling to 64 GT/s, with an intermediate 48 GT/s for design margining and power optimization.

-

Power & efficiency: Runtime recalibration and sideband improvements are meant to improve power efficiency and responsiveness under changing workloads.

-

Topology flexibility: Longer sideband reach supports larger multi-tile arrangements; Raw-Mode mappings support continuous streaming use cases.

-

Adoption path: Backward compatibility preserves 1.0/2.0 investments and eases migration to 3.0-class PHYs and IP.

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center