Chiplets are small, functional integrated circuit (IC) blocks that are designed to work together in a modular fashion to form a complete system-on-chip (SoC) or system-in-package (SiP). Instead of building a large, monolithic chip on a single die, chiplet-based design breaks the system into multiple smaller dies that are connected using advanced packaging and interconnect technologies.

This modular approach enhances design flexibility, yields, scalability, and cost efficiency—especially as traditional silicon scaling (Moore’s Law) becomes increasingly complex and expensive.

Overview

-

Concept: A chiplet is a pre-fabricated silicon die that performs a specific function—such as a CPU core, GPU tile, memory controller, I/O interface, or AI accelerator.

-

Integration: Multiple chiplets are assembled on an interposer or substrate and connected using high-speed interconnects such as UCIe, EMIB, CoWoS, or Foveros.

-

Goal: To reduce the cost and complexity of advanced nodes by enabling heterogeneous integration and mix-and-match architectures.

Background and Motivation

Challenges of Monolithic Chips

-

Cost: Larger dies have exponentially lower yields and higher fabrication costs.

-

Design Complexity: Scaling to advanced process nodes (e.g., 3nm, 2nm) increases development time and risk.

-

Feature Integration: Mixing analog, digital, RF, memory, and specialized compute on one die is inefficient.

Chiplet Advantages

-

Yield Improvement: Smaller dies reduce defect-related losses.

-

IP Reuse: Proven chiplets can be reused across multiple products and platforms.

-

Node Optimization: Designers can use different process nodes for different chiplets (e.g., logic at 3nm, I/O at 28nm).

-

Customization: Easier to configure different product variants from a common chiplet library.

Technology and Interconnect Standards

Several interconnect technologies enable chiplet communication:

-

UCIe (Universal Chiplet Interconnect Express): Industry-standard open die-to-die interconnect promoted by Intel, AMD, TSMC, ASE, and others.

-

AMD Infinity Fabric: Proprietary high-bandwidth interconnect used across AMD chiplets.

-

Intel EMIB (Embedded Multi-Die Interconnect Bridge): Allows side-by-side die placement with high-speed links.

-

TSMC CoWoS (Chip-on-Wafer-on-Substrate): Advanced 2.5D packaging for high-bandwidth connections.

-

Intel Foveros: 3D stacking technology for vertical chiplet integration.

Applications

Chiplets are widely used across many semiconductor domains:

-

High-Performance CPUs and GPUs: AMD’s Ryzen and EPYC processors use chiplets for CPU cores, cache, and I/O.

-

AI and ML accelerators: NVIDIA, Intel, and startups use chiplets for scalability and memory integration.

-

Networking: Chiplets integrate high-speed transceivers, DSPs, and control logic.

-

Heterogeneous Computing: Enables mixing CPUs, GPUs, FPGAs, and custom logic in a single package.

-

Defense and Aerospace: Facilitates modular upgrades and radiation-hardened designs.

Industry Adoption

Major Companies Using Chiplets

-

AMD: A pioneer in chiplet-based x86 processors.

-

Intel: Uses EMIB and Foveros in Xeon, Lakefield, and future designs.

-

TSMC: Provides CoWoS, InFO, and UCIe-based packaging for customers.

-

Apple: M-series chips may evolve toward chiplet-style architectures for scalability.

-

NVIDIA: Leverages advanced packaging in HPC and AI applications.

-

Tenstorrent, Cerebras, and Esperanto: AI startups using chiplets to scale compute efficiently.

Standards and Ecosystem

UCIe Consortium

Founded in 2022, the Universal Chiplet Interconnect Express (UCIe) Consortium includes major industry players aiming to standardize die-to-die connectivity to enable a broader chiplet ecosystem.

UCIe defines:

-

Electrical signaling

-

Protocol stacks

-

Die-to-die PHY and link layer

-

System software integration

The vision is to create an open ecosystem where chiplets from different vendors can interoperate like components in a PCB system.

Challenges and Considerations

While chiplets offer many advantages, they also introduce challenges:

-

Design Complexity: Requires advanced packaging co-design, thermal modeling, and simulation.

-

Interoperability: Standardization is essential for multi-vendor integration.

-

Yield Coupling: While small chiplets improve yield, the package is only functional if all dies work.

-

Thermal Management: Denser packages need effective cooling strategies.

-

Software and System Integration: Ensuring seamless OS, driver, and application support for multi-die systems.

Future Outlook

Chiplets are seen as a foundational element for the post-Moore’s Law era. As scaling slows, architects are increasingly turning to system-level innovation, where chiplet-based SoCs provide:

-

Better performance per watt

-

Faster time to market

-

More flexible customization

The future may see an open marketplace of chiplets, where SoC designers can mix and match IPs from different vendors, much like assembling LEGO blocks, enabling faster and cheaper innovation across industries.

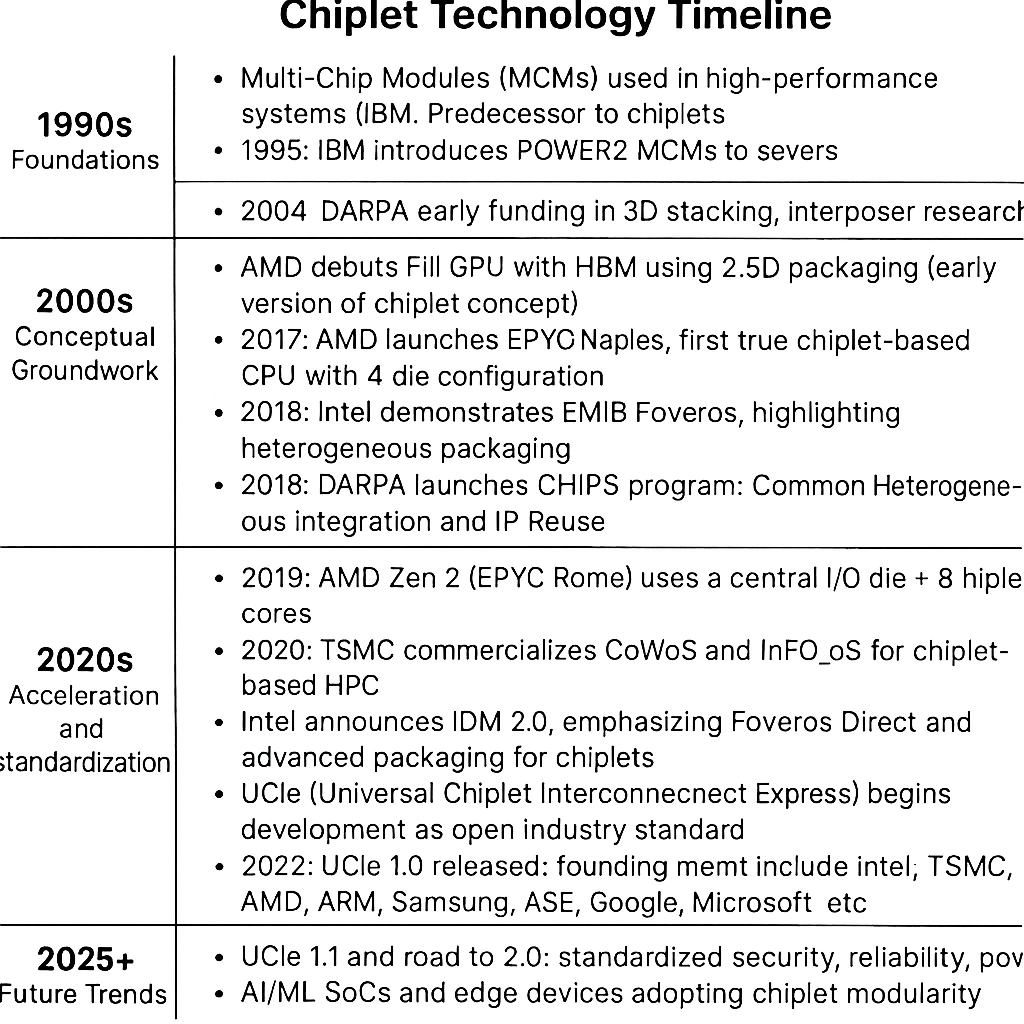

🧩 Chiplet Technology Timeline

1990s: Foundations

-

1990s – Multi-Chip Modules (MCMs) used in high-performance systems (e.g., IBM, DEC). Predecessor to chiplets.

-

1995 – IBM introduces POWER2 MCMs for servers.

2000s: Conceptual Groundwork

-

2004 – DARPA begins early funding in 3D stacking and interposer research.

-

2008 – Xilinx and others explore 2.5D integration with passive interposers.

2010s: Chiplet Concept Emerges

-

2015 – AMD debuts Fiji GPU with HBM using 2.5D packaging (early version of chiplet concept).

-

2017 – AMD launches EPYC Naples, the first true chiplet-based CPU with 4 die configuration.

-

2018 – Intel demonstrates EMIB and Foveros, highlighting heterogeneous packaging.

-

2018 – DARPA launches CHIPS program: Common Heterogeneous Integration and IP Reuse.

2020s: Acceleration and Standardization

-

2019 – AMD Zen 2 (EPYC Rome) uses a central I/O die + 8 chiplet cores.

-

2020 – TSMC commercializes CoWoS and InFO_oS for chiplet-based HPC.

-

2021 – Intel announces IDM 2.0, emphasizing Foveros Direct and advanced packaging for chiplets.

-

2021 – UCIe (Universal Chiplet Interconnect Express) starts development as an open industry standard.

-

2022 – UCIe 1.0 released; founding members include Intel, TSMC, AMD, ARM, Samsung, ASE, Google, Microsoft, etc.

-

2022 – AMD Ryzen 7000 and EPYC Genoa use advanced chiplet architecture.

-

2023 – Intel’s Meteor Lake (client CPU) launches with tile-based architecture and Foveros 3D stacking.

-

2023 – NVIDIA adopts multi-die architecture in Grace Hopper and Blackwell platforms.

-

2024 – TSMC, Samsung, and Intel all announce major UCIe test platforms and chiplet ecosystems.

2025+: Future Trends

-

UCIe 1.1 and road to 2.0: standardized security, reliability, power.

-

AI/ML SoCs and edge devices adopting chiplet modularity.

-

Defense and automotive sectors investing in trusted heterogeneous integration.

-

3D IC + chiplets becoming dominant paradigm in HPC and cloud compute.

https://semiwiki.com/category/chiplet/

Share this post via:

The Semiconductor Growth Numbers are Insane but the Real World Doesn’t Tally!