Defacto Technologies

Type: Private

Industry: Electronic Design Automation (EDA), RTL SoC Integration & Verification

Founded: 2003 (originating from R&D at Grenoble, France) Minalogic+10SemiWiki+10Design Reuse+10

Headquarters: Grenoble/Moirans area, French Alps, France (with a U.S. branch in California)

CEO / Managing Director: Dr. Chouki Aktouf (Co‑founder and key technical leader)

🎯 Overview

Defacto Technologies delivers a unified RTL “Build & Signoff” platform—STAR SoC Compiler—that automates front‑end SoC integration, optimization, verification, and signoff flows. It is designed to manage IP insertion, power and design constraints (UPF, SDC, LEF/DEF, IP-XACT), and structural checks in RTL, allowing significant reductions in time and engineering effort across complex SoC projects. Minalogic+9Design Reuse+9DATE 2021+9

🛠 Products & Solutions

STAR SoC Compiler

-

Automates multi-format IP insertion and SoC connectivity generation based on user specifications.

-

Offers structural verifications: connectivity, clock domain, feed-through, and more—without relying on gate-level design.

-

Supports RTL restructuring for PPA optimization (area, performance, power)—achieves layout density improvements of ~5–10%. SemiWiki+1DATE 2021+1SemiWiki+2Design Reuse+2DATE 2021+2

Unified Dataflow & Design APIs

-

Supports IP-XACT, UPF, SDC, LEF/DEF, Liberty and other standard formats.

-

Enables Python/Tcl scripting for highly programmable SoC flows.

-

Allows custom tools through open APIs over a unified RTL database.

RTL-Level Verification & Checks

-

Embedded linting and verification for VHDL, Verilog, and SystemVerilog.

-

Consistency checks across multiple RTL views and design constraints.

-

In-line Design-for-Test (DFT) checks and IP signoff at RTL stage. DATE 2021+2SemiWiki+2Design Reuse+2Tracxn

📜 History & Origins

-

1997: Dr. Chouki Aktouf begins research on RTL-level Design-for-Test (DFT) methodologies at Grenoble’s INPG (France), pioneering RTL DFT validation. Minalogic+4SemiWiki+4DATE 2021+4

-

2003: Formal founding of Defacto Technologies as a spin-off from academic research. Aktouf becomes CEO alongside partners. Early funding came from CM‑CIC Capital Innovation and Innovacom. DATE 2021+4SemiWiki+4Tracxn+4

-

2005–2008: Launched RTL DFT toolset and formally introduced STAR – RTL Build & Signoff platform for structural optimization, connectivity analysis, power-intent checking, and IP integration. linkglobal21+5SemiWiki+5DATE 2021+5

📈 Recent Developments

-

April 2025: Released updated SoC Compiler supporting automated front-end integration for complex RISC‑V designs, with enhancements in RISC‑V IP library, linting, and PPA restructuring. Presented at RISC‑V Summit, Paris. Defacto Tech+5Design Reuse+5Defacto Tech+5

-

Featured at DAC 2025 (#62DAC), showcasing SoC Compiler Release and use case demos. Defacto Tech+2SemiWiki+2Design Reuse+2

🌍 Markets & Industry Partnerships

-

Strong global presence serving automotive, mobile, AI, VR, and semiconductor sectors, supporting companies in the U.S., Europe, Asia, and beyond. 24/7 support is provided internationally. Defacto Tech+1linkglobal21+1

-

Recognized partner in ARM’s ecosystem as a certified Arm tools partner, visible in Arm partner catalog and solution briefs. SemiWiki+2ARM+2Minalogic+2

🧠 Strategic Differentiators

-

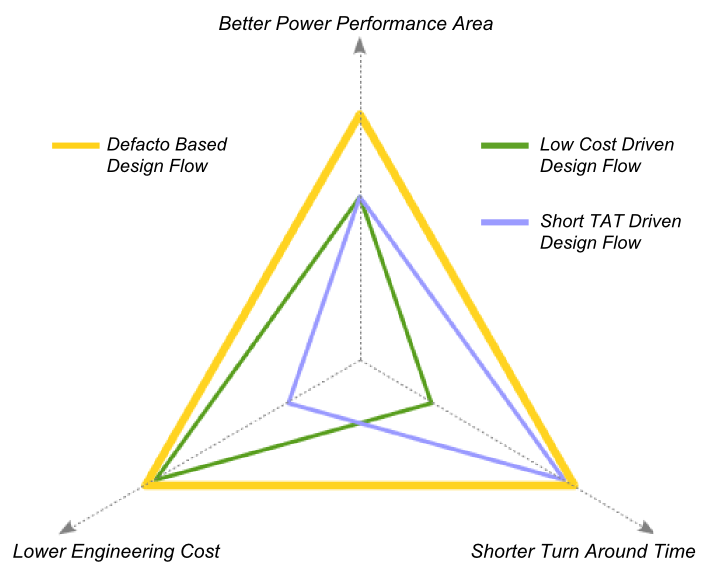

RTL-level SoC design signoff with automation, customization, and optimization—increasing design closure speed and reducing manual scripting.

-

Unified RTL database supporting multiple design and constraint formats, enabling cross-domain consistency.

-

Highly programmable, open API model for customer-specific automation and in-house extensions.

-

Strong adoption for RISC‑V-based SoC integration, leveraging built-in IP libraries and automation for next-gen architectures. DATE 2021+4Design Reuse+4SemiWiki+4

📋 Summary Table

| Category | Details |

|---|---|

| Founded | 2003 (spin‑off from Grenoble INPG research, 1997–2003) |

| Headquarters | Grenoble/Moirans (France); U.S. branch in California |

| Founder & CEO | Dr. Chouki Aktouf |

| Flagship Product | STAR SoC Compiler (RTL Build & Signoff platform) |

| Key Capabilities | IP insertion, RTL verification, PPA optimization, structural checks |

| Supported Standards | IP-XACT, UPF, SDC, LEF/DEF, Liberty, Verilog, UVM |

| Target Architecture Focus | RISC‑V, ARM-based SoCs, high‑complexity RTL platforms |

| Core Benefits | Automation, reusability, design quality, reduced time‑to‑market |

Defacto Technologies on SemiWiki

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.