Earlier this week it was the Synopsys user group meeting SNUG. Not just any old SNUG but the 25th Annual SNUG. The first one was 15th March 1991 and was attended by 100 people. At the time, Synopsys had annual revenues of $22M. This year, the various SNUGs around the world will have a total attendance of 10,000 people and Synopsys revenue is $2.2B.

Aart de Geus, co-CEO of Synopsys, gave the keynote as usual. Since it was the same Shift Left keynote as he gave earlier at DVCon that Dan already wrote about, I won’t cover it in detail.

See also Shifting Chip Design Left

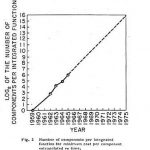

But as Aart pointed out, there is an even more important anniversary coming up in 28 days (down to 25 now), the 50th anniversary of Moore’s Law. In Electronics Magazine on April 19th 1965 Gordon Moore (at the time still at Fairchild) published an article titledCramming more components onto integrated circuits. Everyone in semiconductors knows what Moore said about doubling of transistors and probably have seen the original graph that he published in the article. What I think is perhaps even more amazing is that the second paragraph of his article said:Integrated circuits will lead to such wonders as home computers…automatic controls for automobiles, and personal portable communications equipment.

Remember, this was 1965. The Beatles were still two years away from putting out Sergeant Pepper. Gordon Moore himself was still 3 years away from founding Intel. Computers filled rooms. Touch-tone phones had not yet been introduced. This was an extraordinary prediction when an integrated circuit did not contain billions of transistors but just 64.

During his keynote, Aart pointed out that he was using the term Moore’s Law in an imprecise sense. I have always liked to use Moore’s Law backwards, namely that the cost of any given functionality implemented in silicon halves every couple of years. That exponential cost reduction means that our smartphones contain much more powerful graphics than a multi-million dollar flight simulator used to.

However, that aspect of Moore’s Law is now broken. Yes, for chips that can make use of it there will be wonderful capabilities at 14/16nm, 10nm, 7nm. Much lower power. Much higher performance. Another factor of 10 in integration. But not lower cost. As FinFet volume manufacturing builds up, perhaps 16nm will eventually be cheaper than 28nm, but for sure not by as much as we have been used to (the rule of thumb used to be twice the number of transistors, 15% increase in wafer cost, so 35% reduction in cost per transistor). That is why so many people are predicting that 28nm will be a very long-lived process. Double patterning (necessary below 28nm) is an impossible additional cost to swallow completely.

One of the new areas of business for Synopsys has been from their Coverity acquisition. One result is that Synopsys have changed the tagline under their logo to From Silicon to Software. Another result of that is that Synopsys themselves have discovered that they have one of the largest code bases around at over 400M lines of code (LoC), around the same number of DNA base-pairs as a mouse. Coverity is about 5% of Synopsys revenue (IP is 25% and the rest is EDA software).

Software development groups are starting to need the same sort of discipline as chip design groups have had for many years. If a chip doesn’t work it costs millions of dollars for a respin, whereas software has a “patch it later” attitude. But as software finds its way into medical devices, cars (not to mention the arrival of IS26262) and, especially, as security moves towards being mission critical, then software has had to adopt similar approaches to quality and testing. After all, what is “fuzzing” apart from another name for “constrained random.”

Aart had 3 lessons from chip design for software:

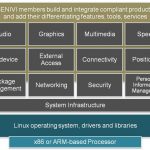

At the press lunch, Aart talked a bit about IP and how a modern process is simply not viable on its own. It doesn’t just need EDA flows and foundation IP like standard cells and memories. It also needs a portfolio of microprocessors, PCI, USB, DDR and so on. Without it only the largest and most advanced SoC groups can think about doing a design since they will need to design all that IP themselves. As a result Synopsys are working on 10nm IP and FD-SOI IP. They already have lots of 10nm active designs.

Aart reminisced that when he was an undergraduate at school in Switzerland everyone just knew that 1um was the ultimate limit for IC design. Well, that day came and went and we are now at 10nm. We can see about another 10 years ahead today, but then that has pretty much always been the case. It will be interesting to see what comes next.

The SNUG 2015 proceedings page is here.